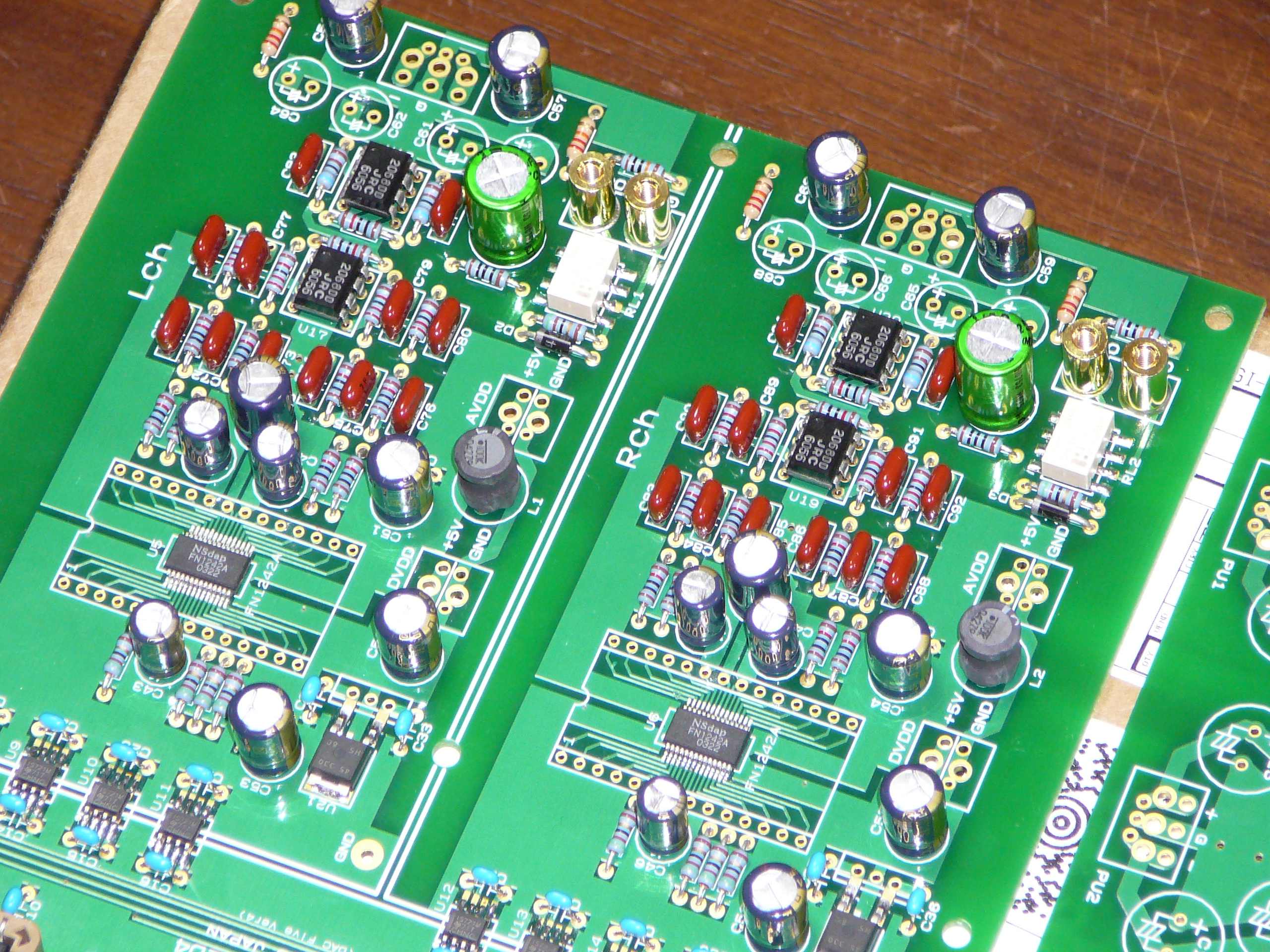

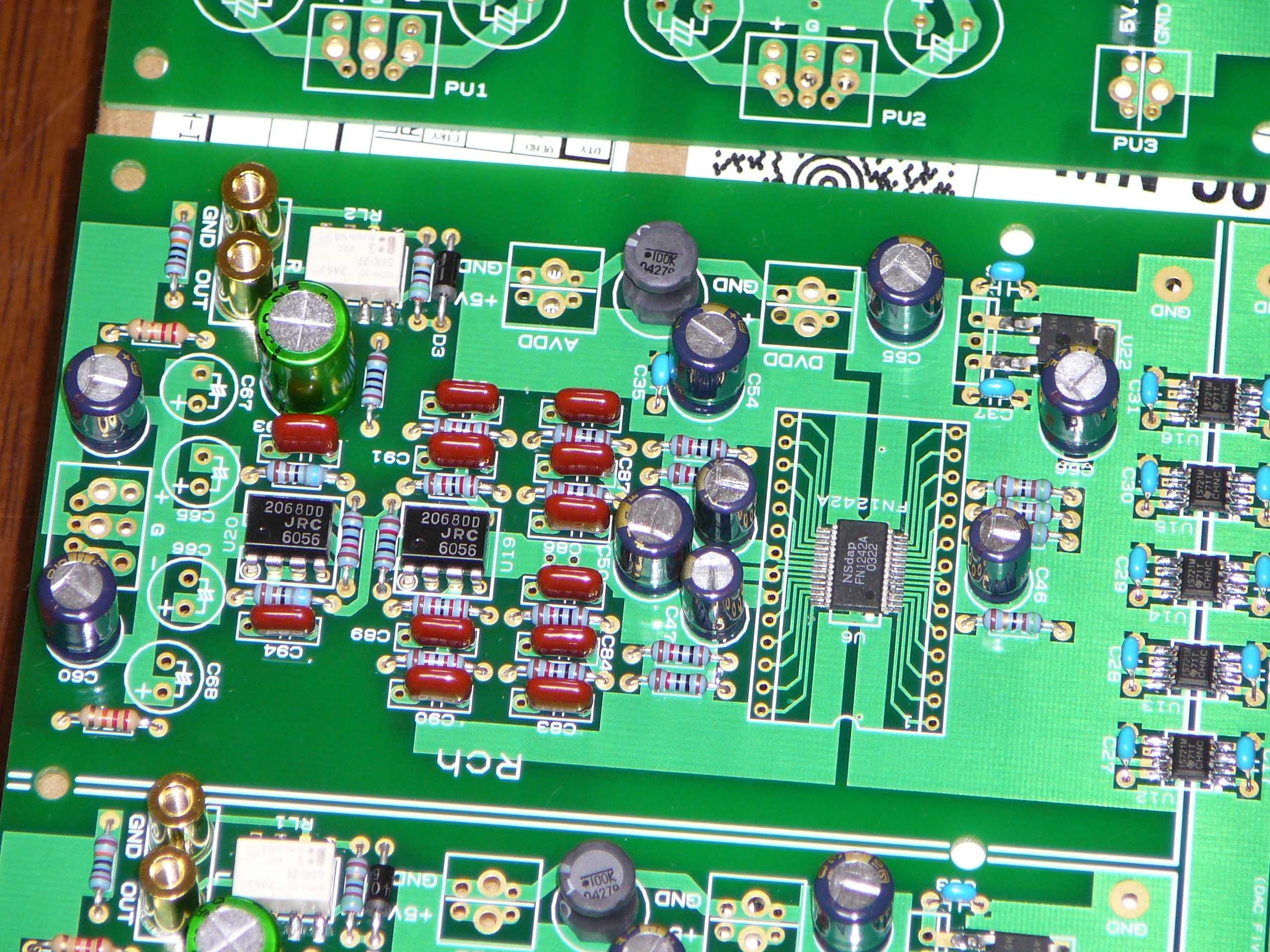

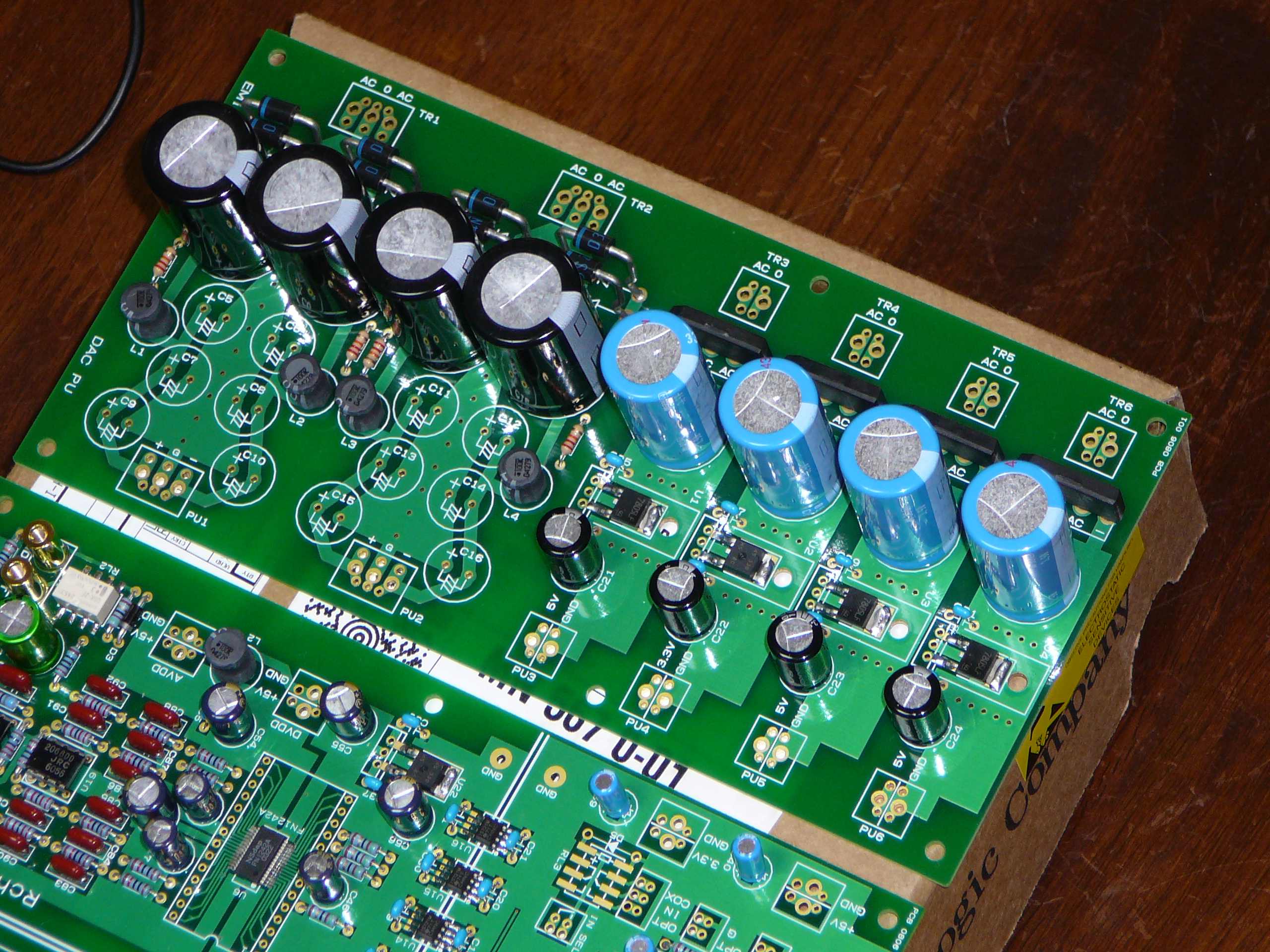

D/A回路図 1/3 2/3 3/3 D/A部品表 D/A部品実装図

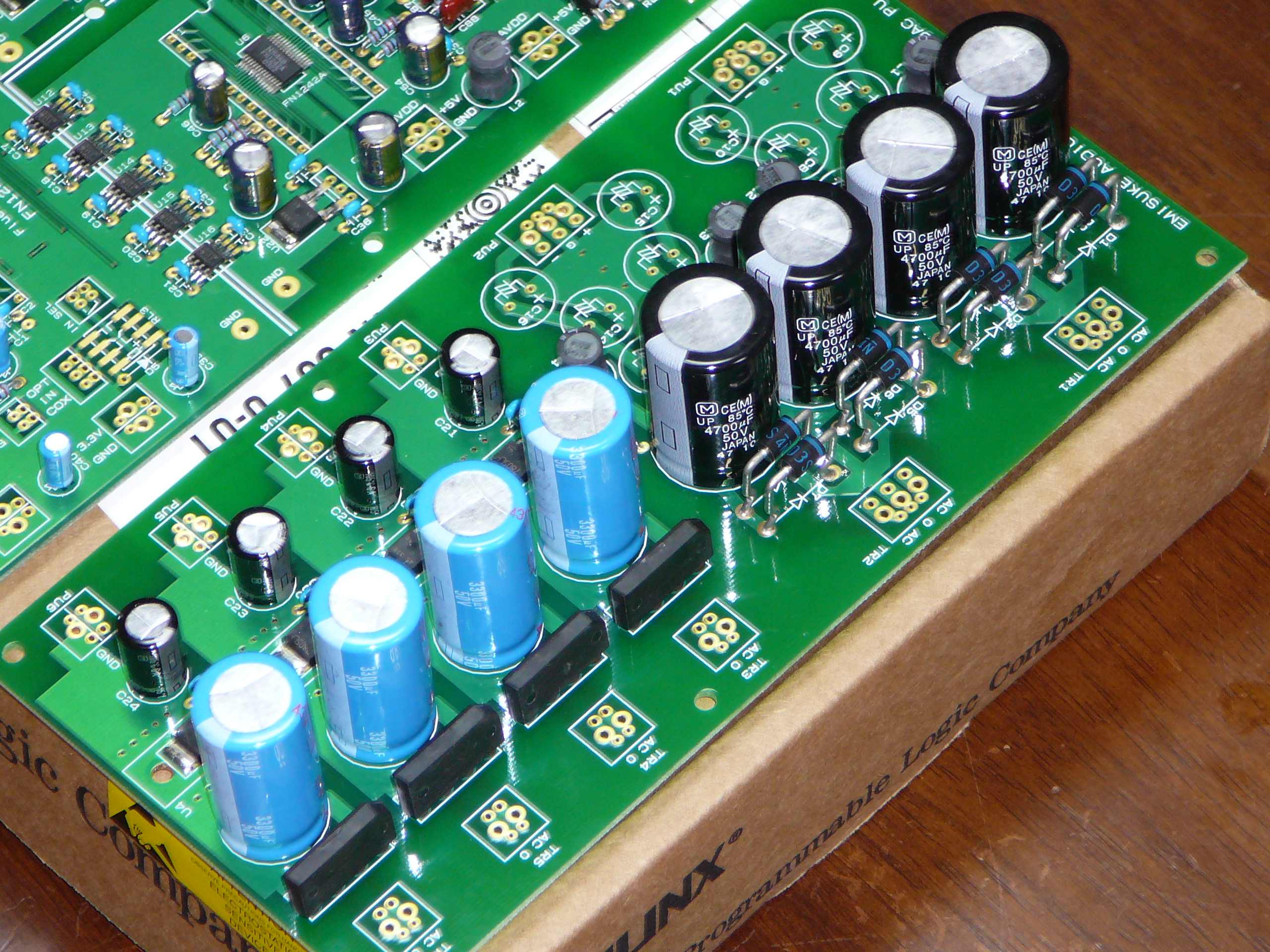

オプション品 TR基板 回路図 部品表 部品実装図

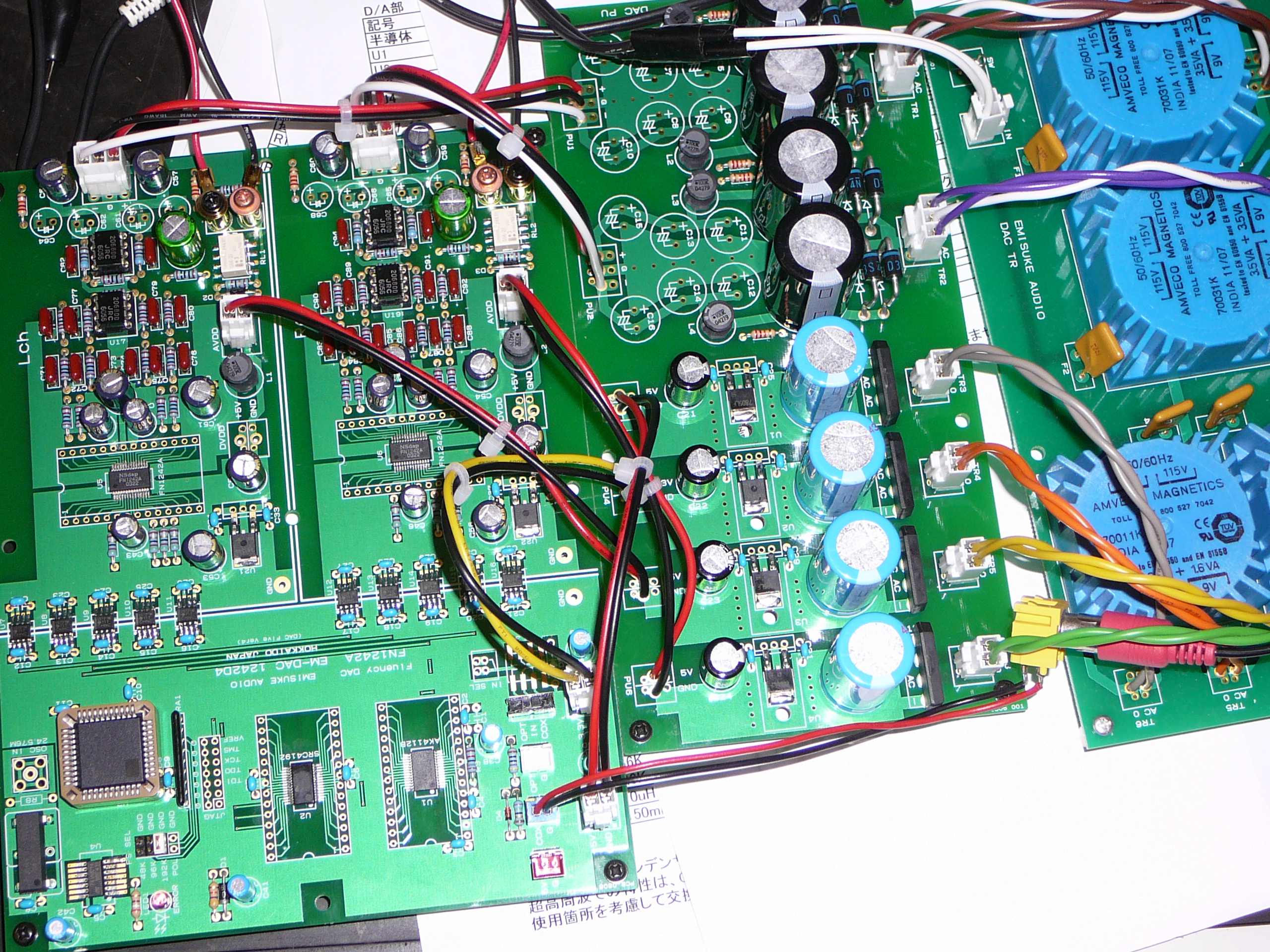

下記写真は、参考用です。

添付部品は、写真と違う場合があります。

データーシート

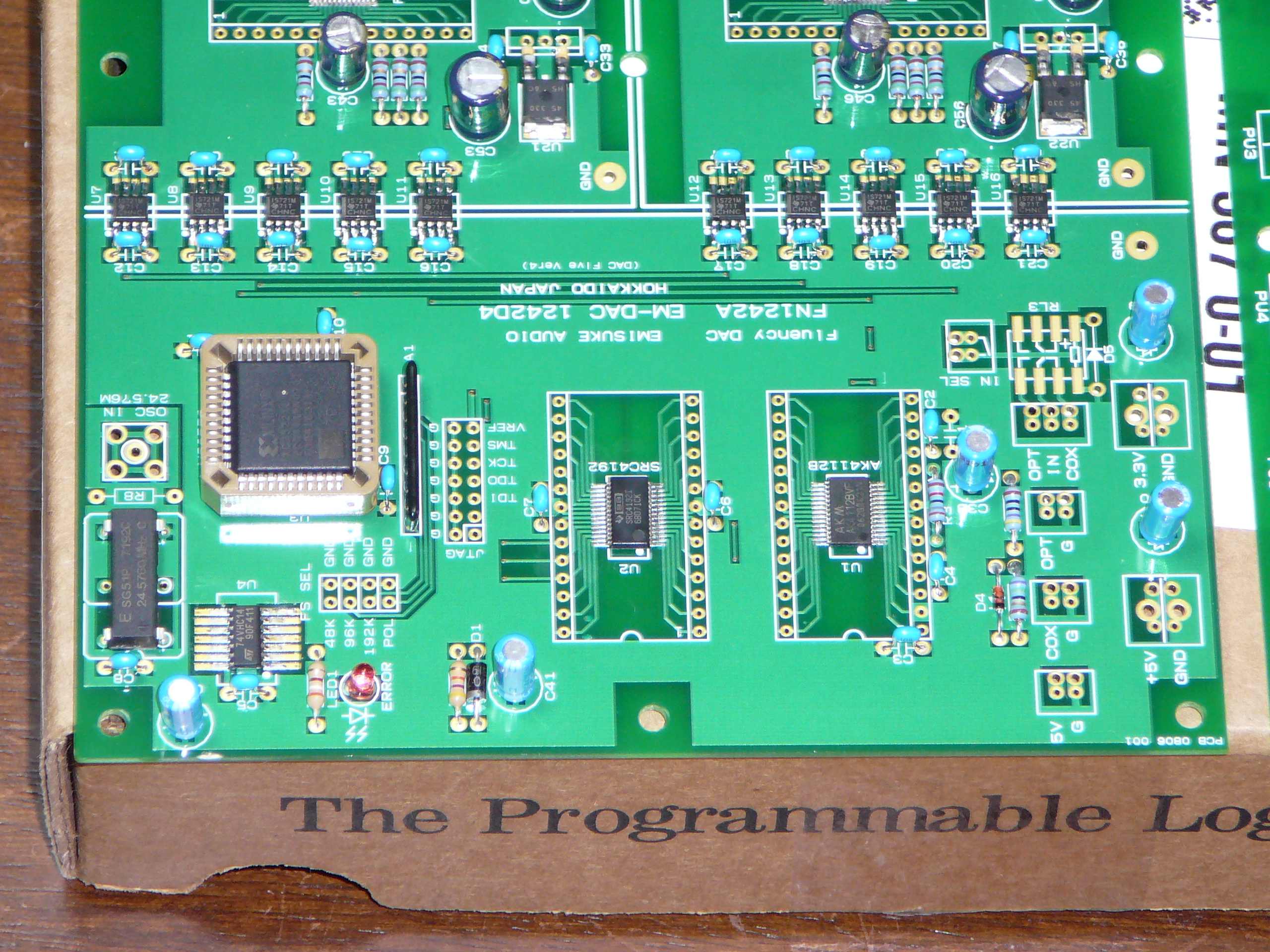

AK4112B

FN1242A

本品は、回路図が理解できて自作ベテラン向けです。

当方は自分用で動作確認済みで、回路図通り組立てれば動作します。

よってベテラン向け配布とし、あえて不動時の質問など受付ない事とします。

不動時は、ご自身の力で解決願います。

掲示板等で聞くのも良いかと思います。

添付している部品数は、200個以上です。

製作難易度は・・・高・・・です。

電源トランスは、整流後、12V以下になる品を使用願います。

三端子レギュレーターの入力耐圧を考慮する必要ありです。

JP設定

D/A基板のFS SEL端子でDA駆動FS周波数を選択します。

48K、96K、192Kどれか一つをショートする必要あり。

未接続時は、48Kが選択されます。

CPLDプログラムの仕様上、設定変更時に電源ON/OFFが必要です。

POL端子は、オープン(未接続)にします。

その他

CPLDの実装方向には十分注意願います。

どの方向にも刺さりますが正規方向以外では当然CPLD破損します。

その他、部品取り付け方向など写真不鮮明箇所は、Webよりデーターシート等を入手して確認願います。

重要部品は、配付数しか手持ち有りません、よってハンダ付け失敗時など代替え品提供不能です。

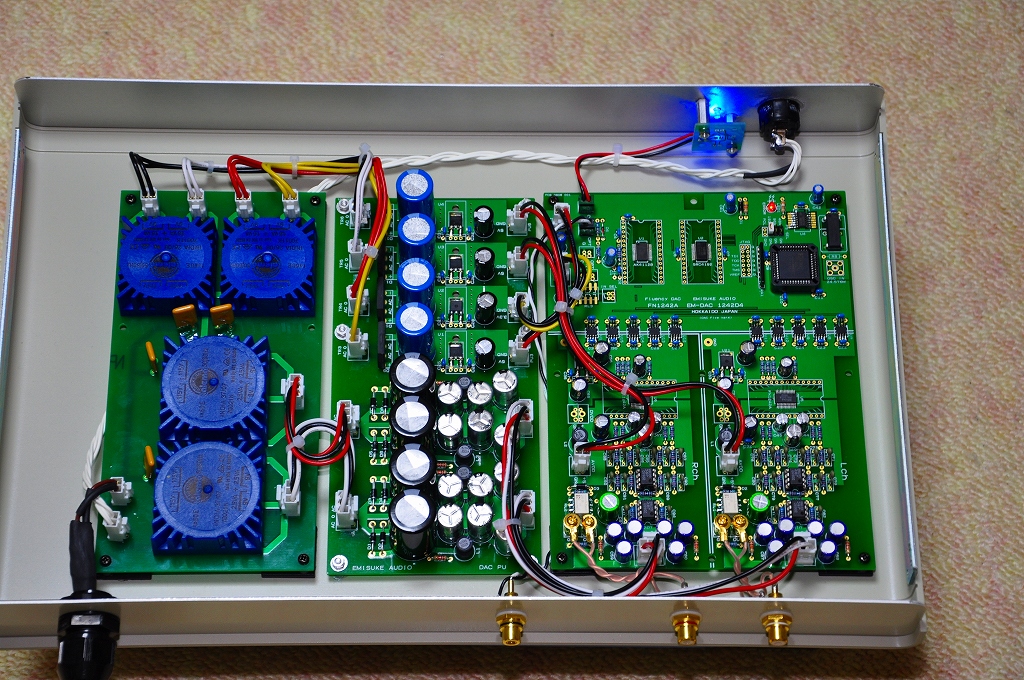

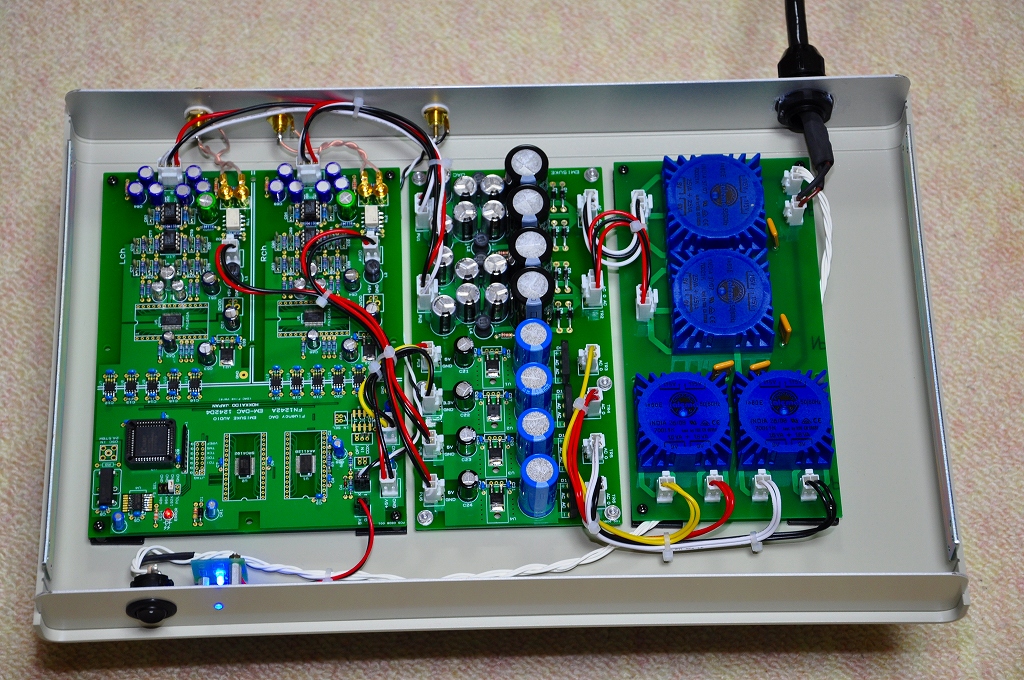

参考写真

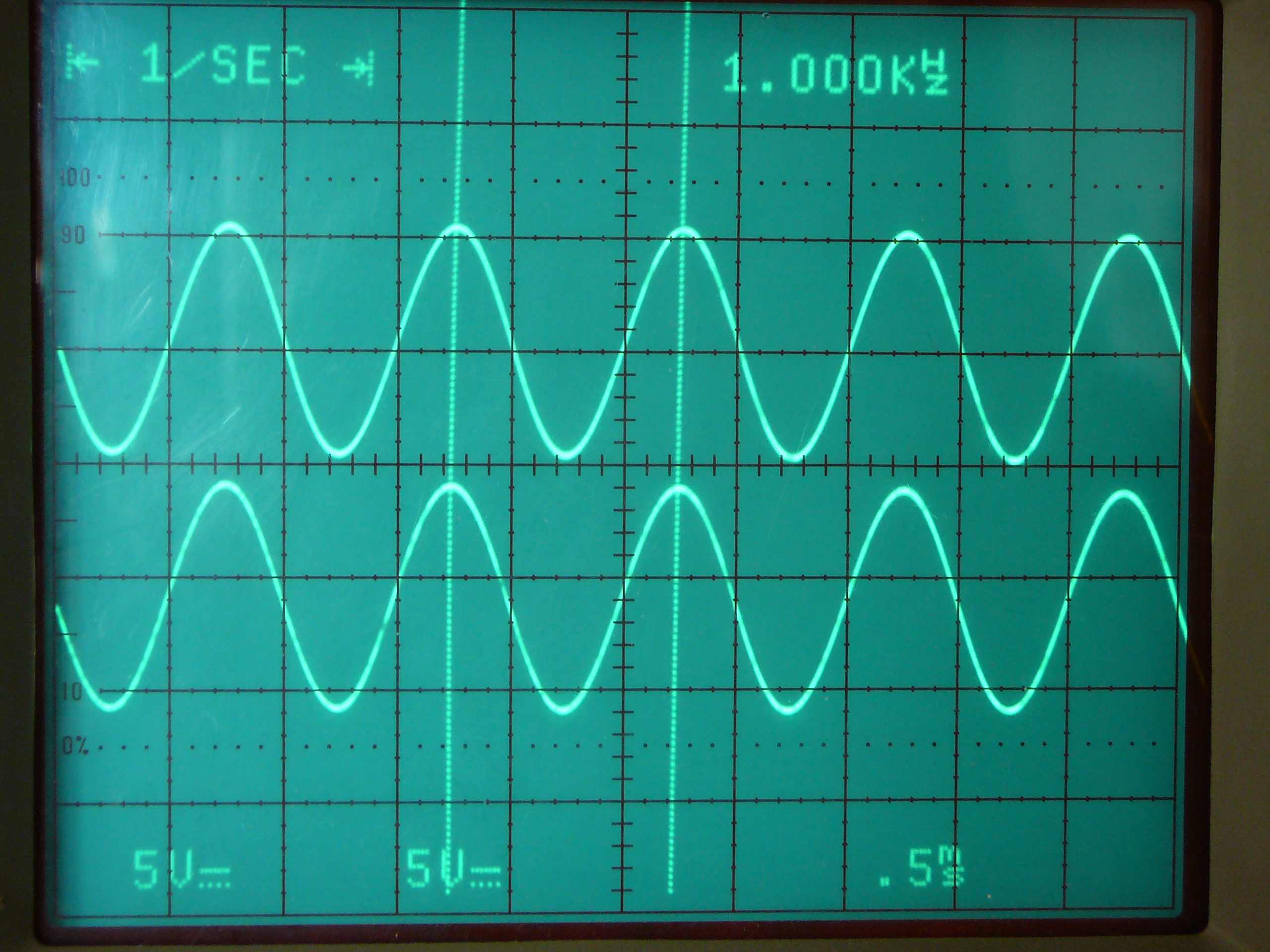

参考 動作確認品での特性

1KHz、0dB入力時

出力電圧 約3.54V(RMS)

ひずみ率 約0.007%

製作例

参考用です。一部使用部品を変更しています。