丂

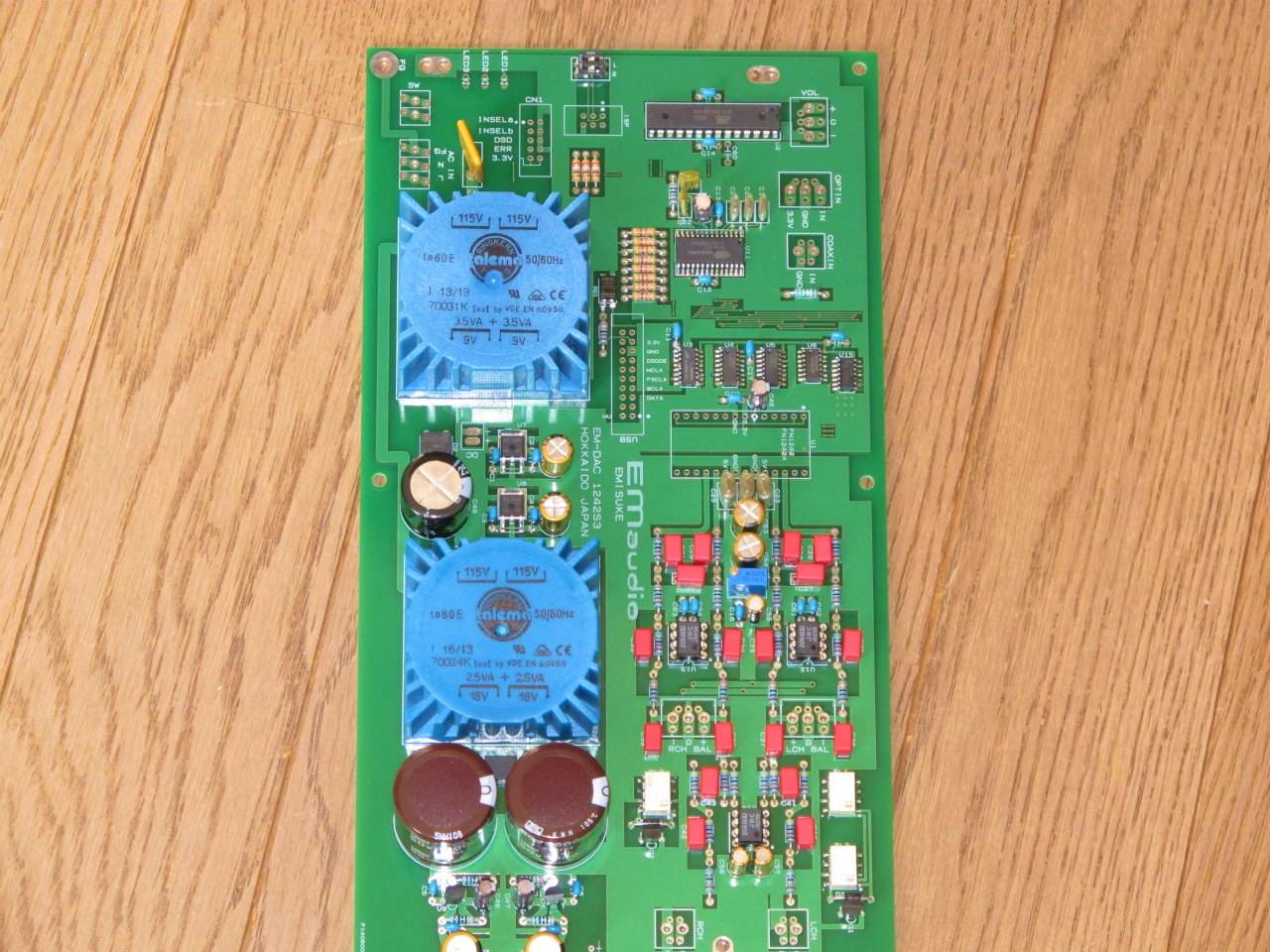

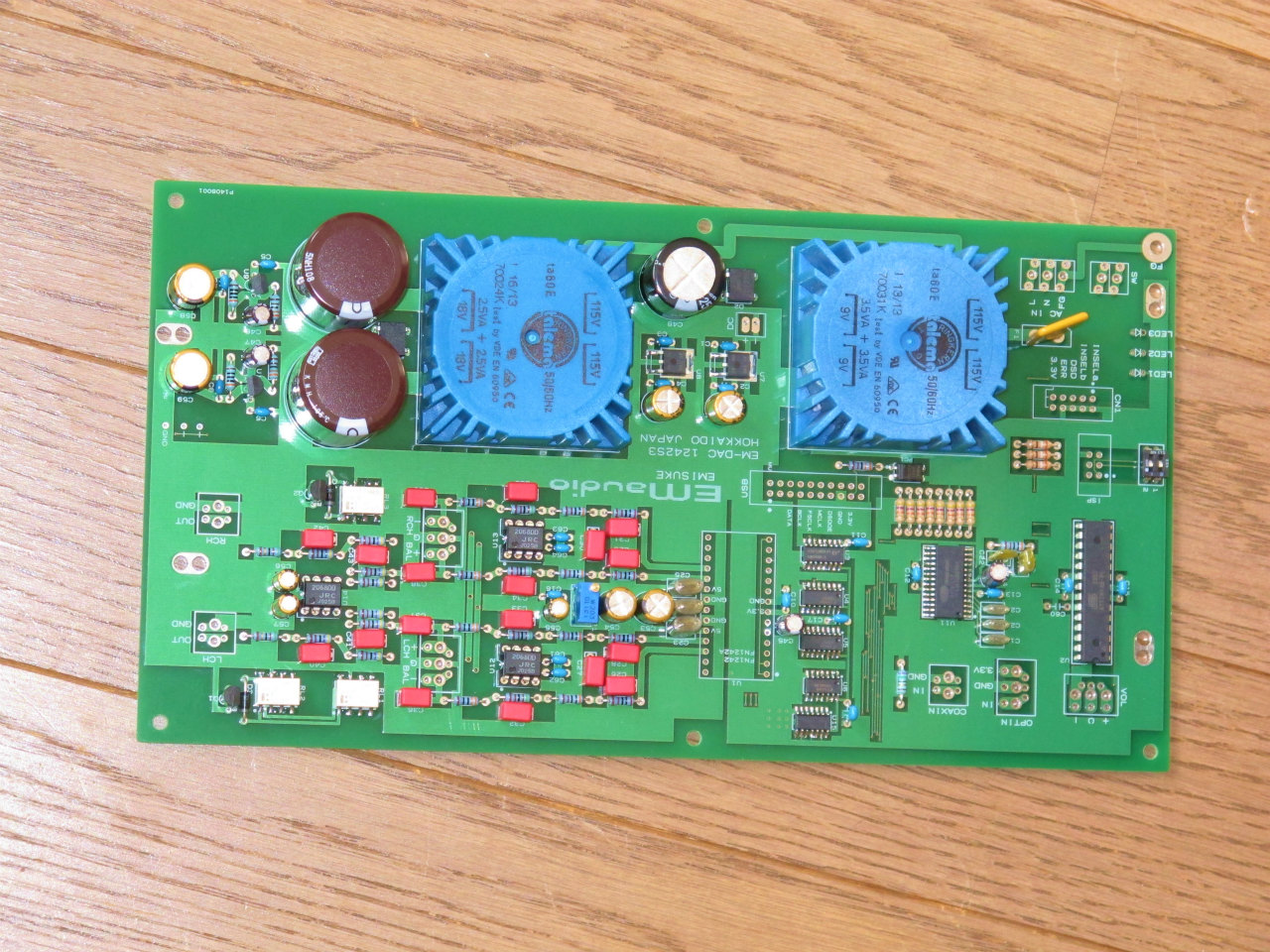

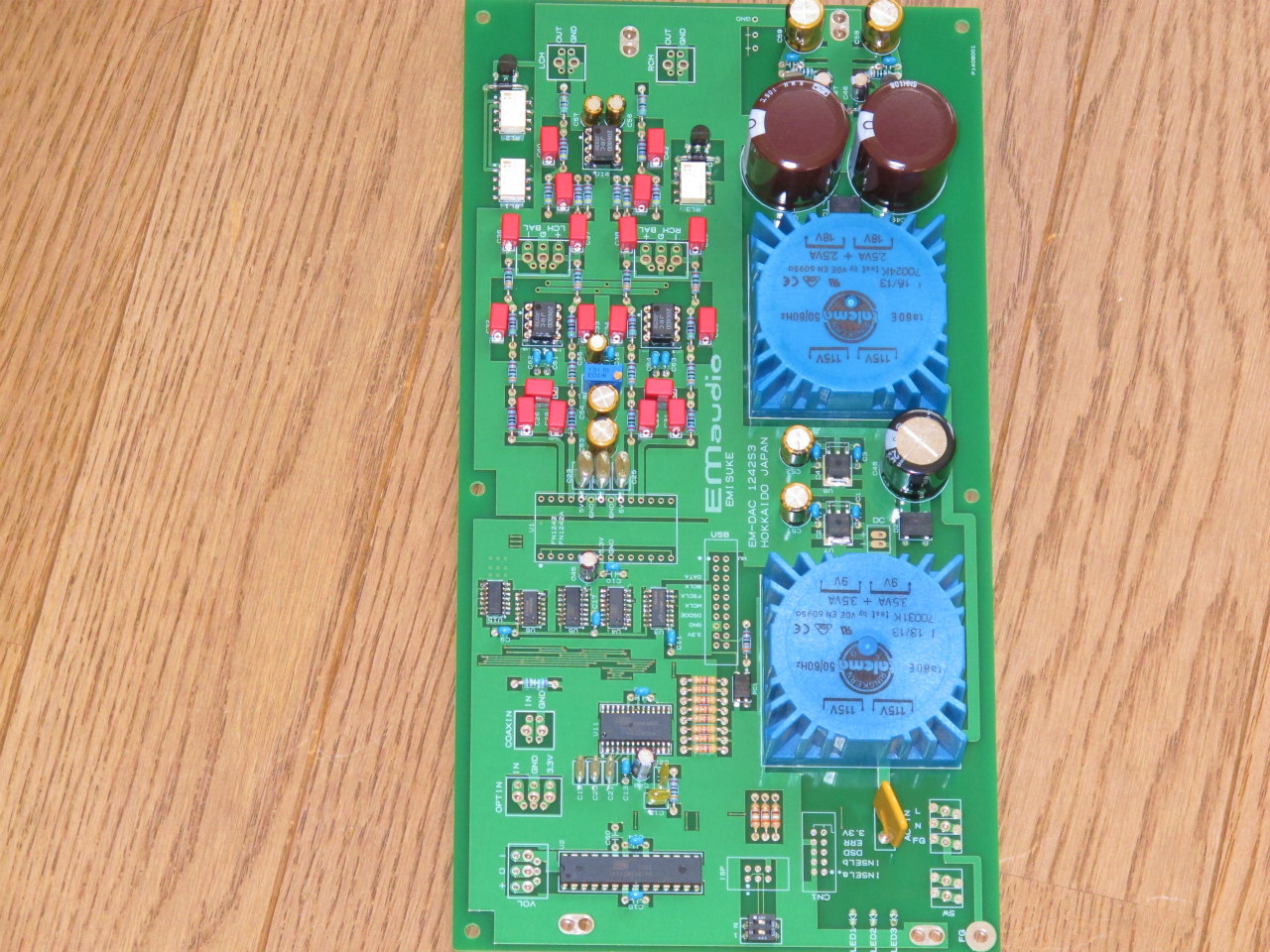

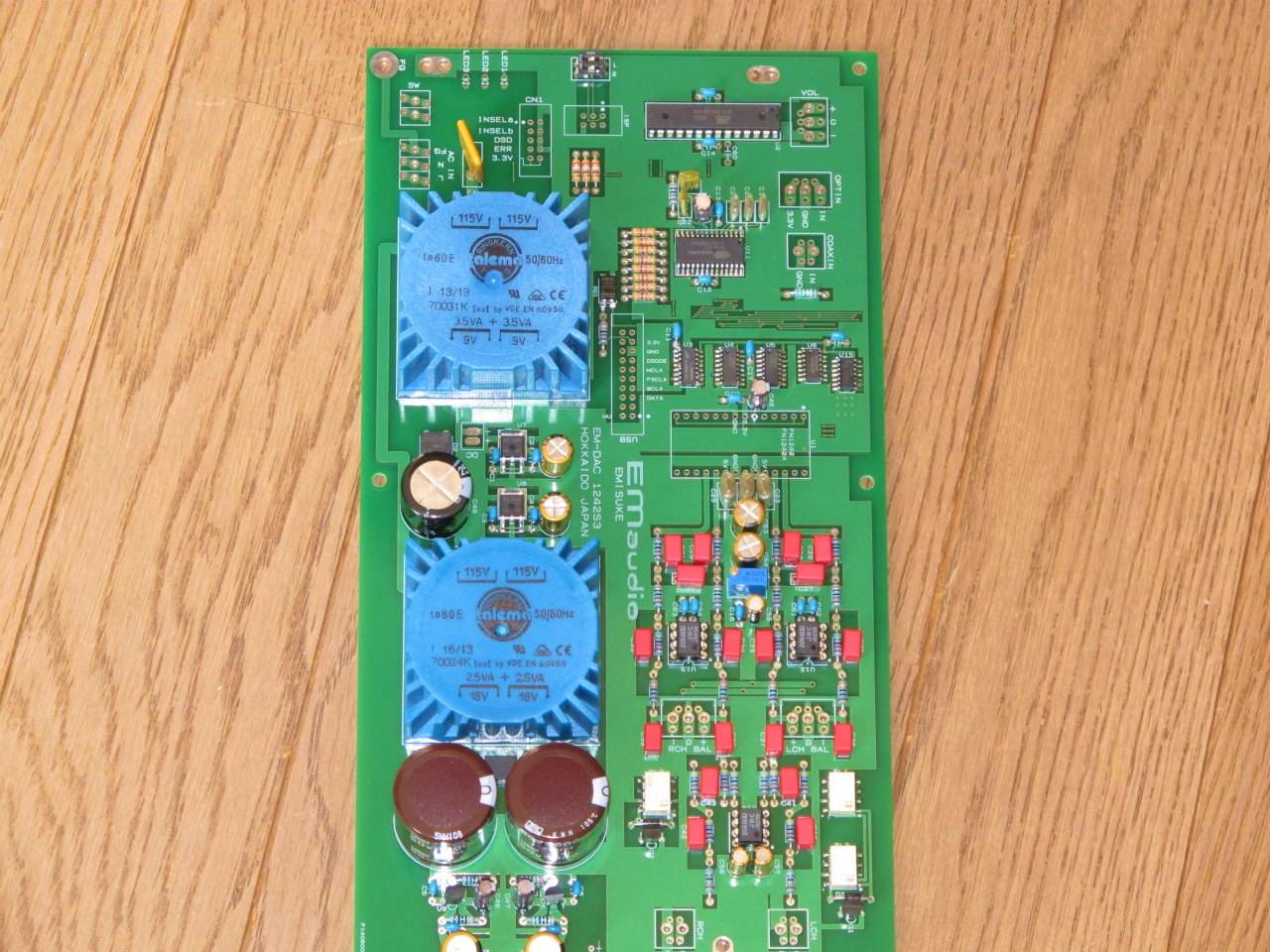

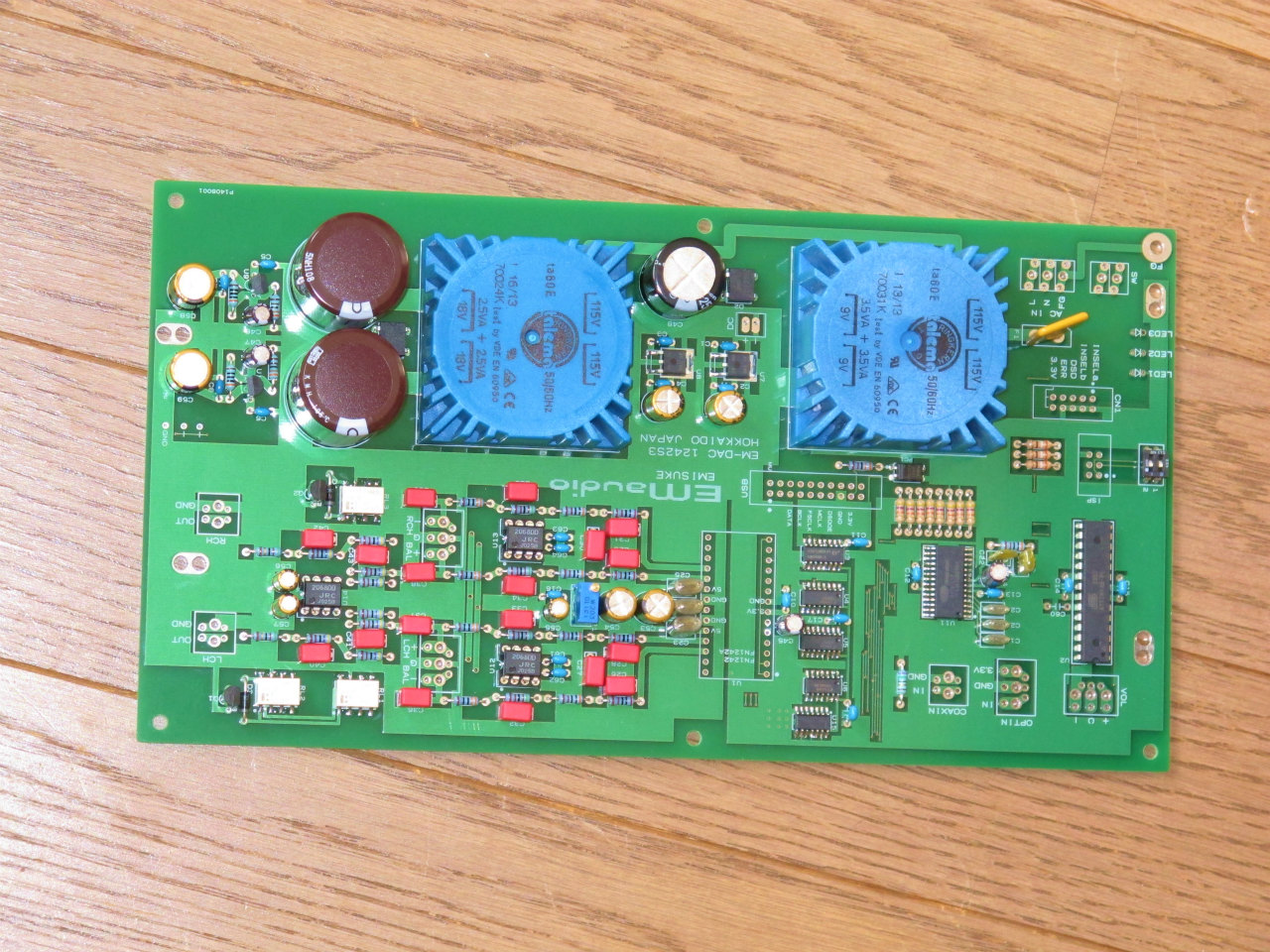

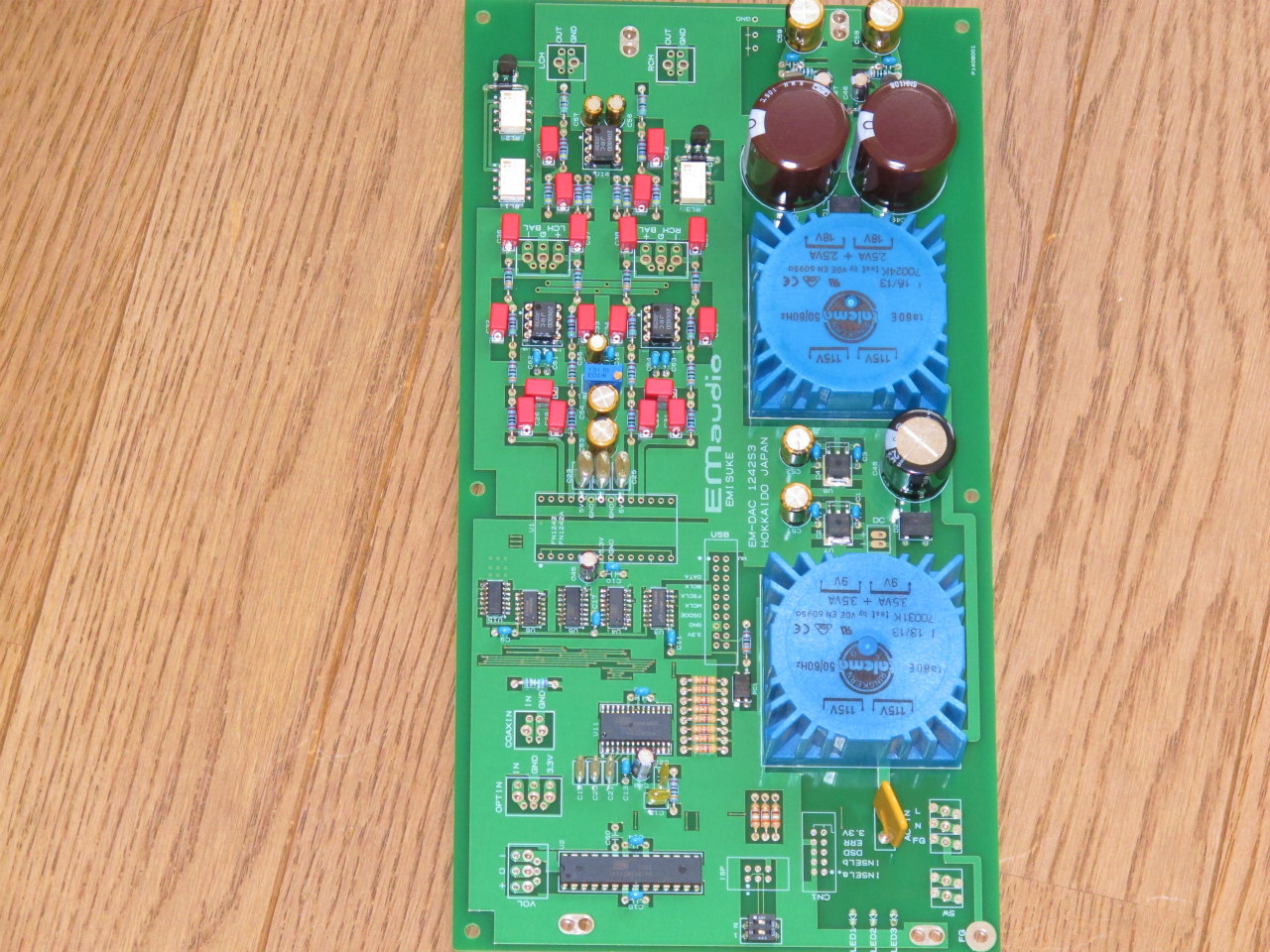

夞楬恾

丂

晹昳昞

丂

晹昳幚憰恾

丂

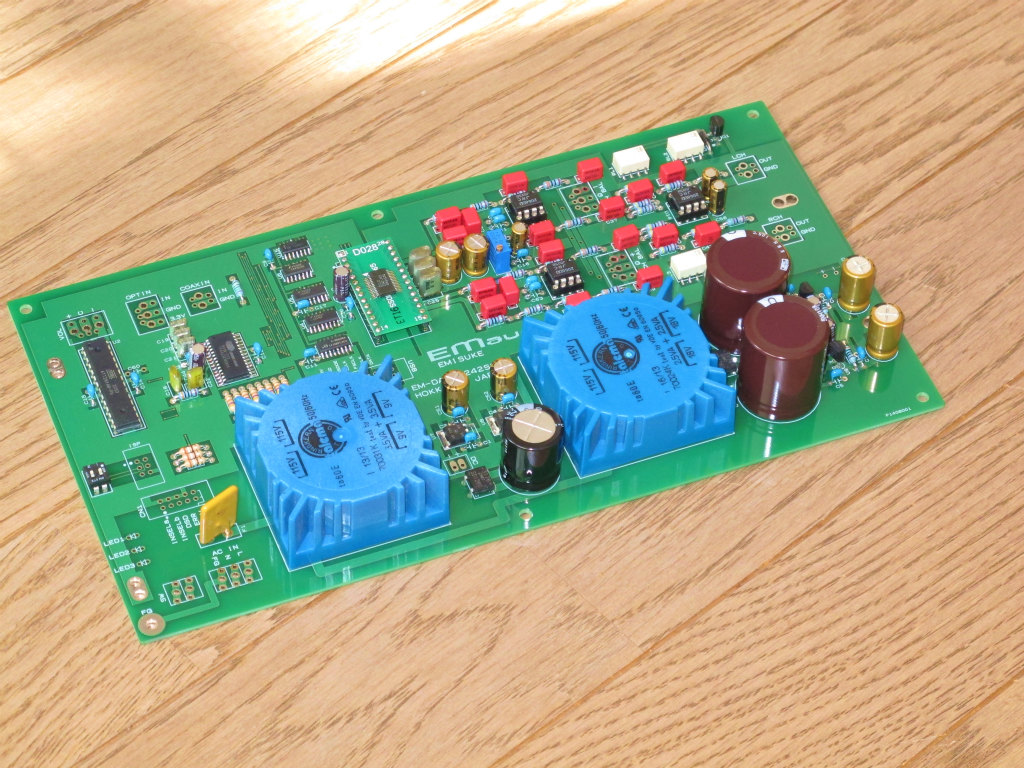

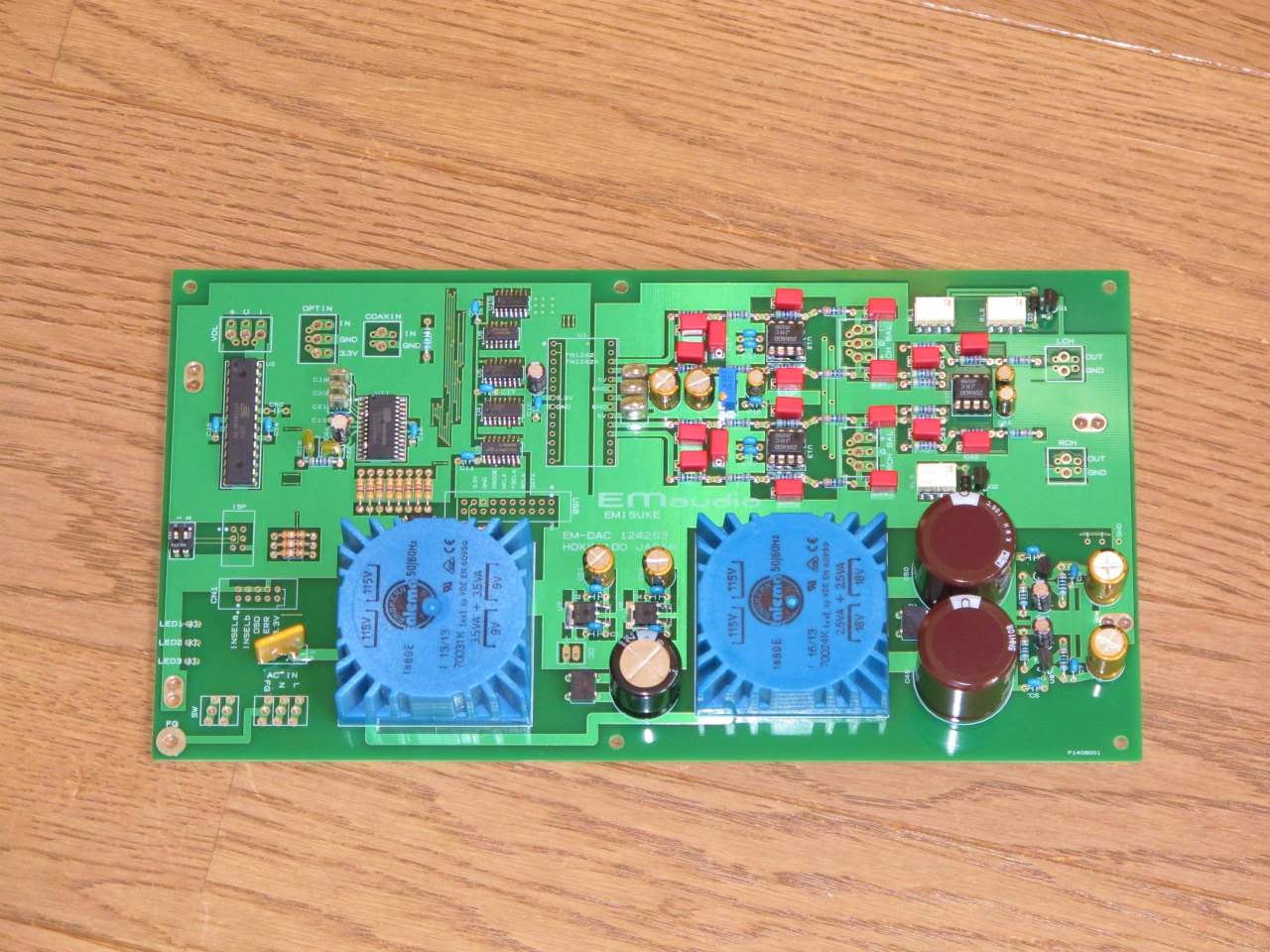

嶲峫寢慄恾

丂枹揧晅晹昳傕幚憰偟偨忬懺幨恀偲側傝傑偡丅堦晹掕悢曄峏偟偰偍傝傑偡丅

丂揧晅晹昳偼丄幨恀偲摨摍惈擻側懠昳偺応崌偑偁傝傑偡丅

丂揧晅晹昳偼丄晹昳昞傪妋擣婅偄傑偡丅

丂丂杮昳偼丄嵟戝尷弶怱幰偱傕慻棫弌棃傞傛偆攝椂偟偨昳偱偡丅

丂丂偨偩偟丄晄摦帪偼夞楬恾偺棟夝偑昁梫偱偡丅

丂丂摉曽偼帺暘梡偱摦嶌妋擣嵪傒偱丄夞楬恾捠傝慻棫偰傟偽摦嶌偟傑偡丅

丂丂晄摦帪偼丄偛帺恎偺椡偱夝寛婅偄傑偡丅

丂

SW愝掕

丂夞楬恾撪偵婰嵹偟偰偍傝傑偡丅

丂

抂巕愢柧

丂夞楬恾丄嶲峫寢慄恾嶲徠

丂

ISP丂CPU彂崬傒梡抂巕乮捠忢帪枹巊梡乯

丂

俠俹倀幚憰

丂FN1242(A)偼丄俠俹倀惂屼偱僨乕僞乕愝掕偝傟偰惓忢偵壒偑弌傑偡丅

丂傛偭偰丄俠俹倀晄椙丄枹幚憰偱偼惓忢摦嶌偟傑偣傫丅

丂

CPU婲摦

丂壒偑弌側偄応崌俋俋亾偼丄俠俹倀埲奜偺晄椙偩偲巚偄傑偡丅乮揹婍婡婍側偺偱侾侽侽亾偱偼柍偄偱偡偑乯

丂壓婰偑妋擣弌棃偨応崌丄俠俹倀偼摦偄偰偄傑偡丅

丂俬俶俽俤俴抂巕偱丄俷俹俿慖戰帪亖俠俹倀俀侾斣抂巕丂俴乮侽倁乯丄俠俷俙倃慖戰帪亖俫乮俁丏俁倁乯偲曄壔偡傞丅

丂

慻棫拲堄揰

丂

晹昳幚憰曽岦偵偼廫暘拲堄婅偄傑偡丅

丂晄嬶崌偱揹尮揹埑偑堎忢偺応崌晹昳攋懝偵偮側偑傝傑偡丅

丂攚偺掅偄晹昳傛傝庢晅偰偄偒傑偡丅

丂嵟弶偵昞柺幚憰晹昳傪庢晅傑偡丅

丂

丂

丂

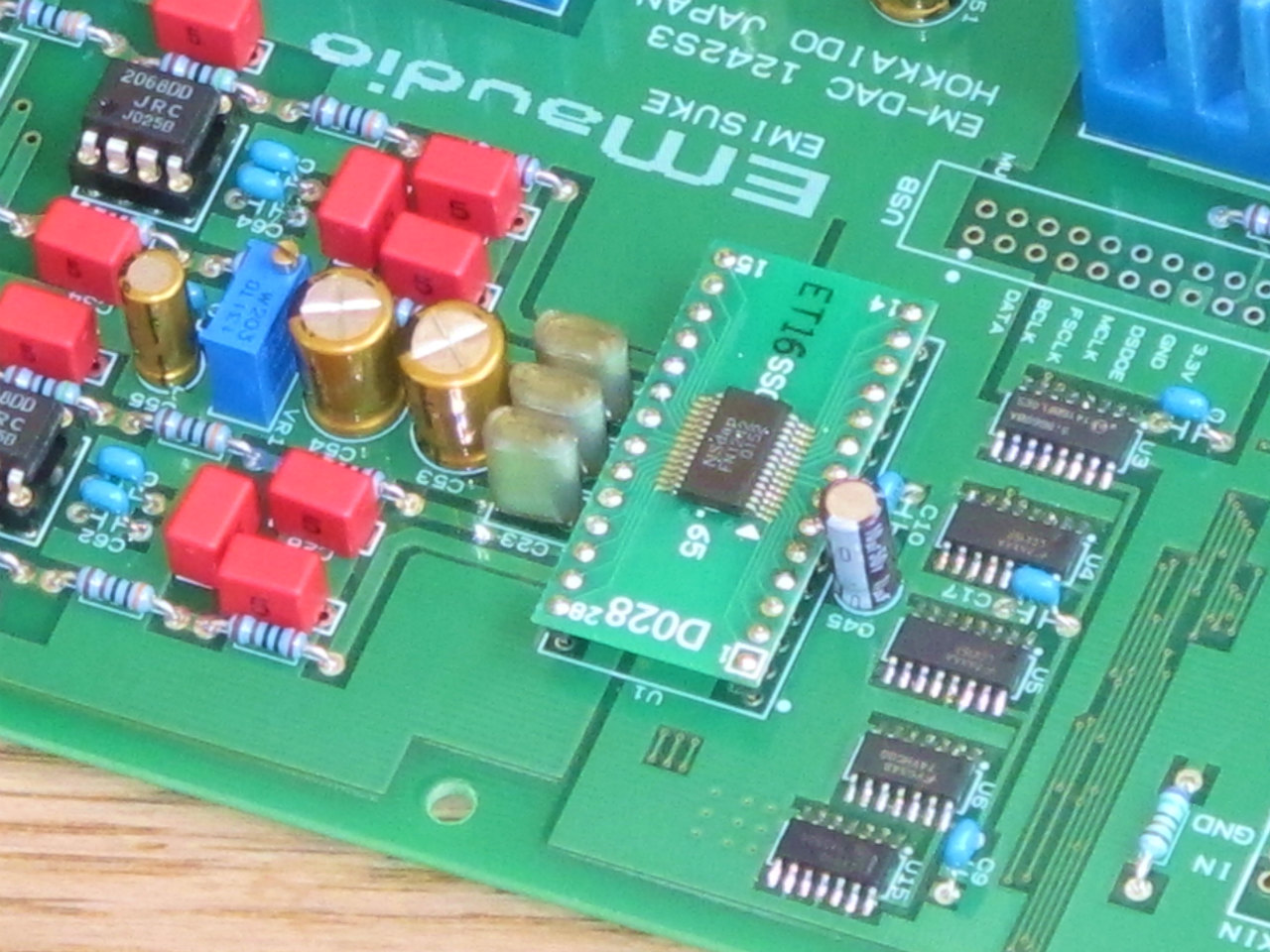

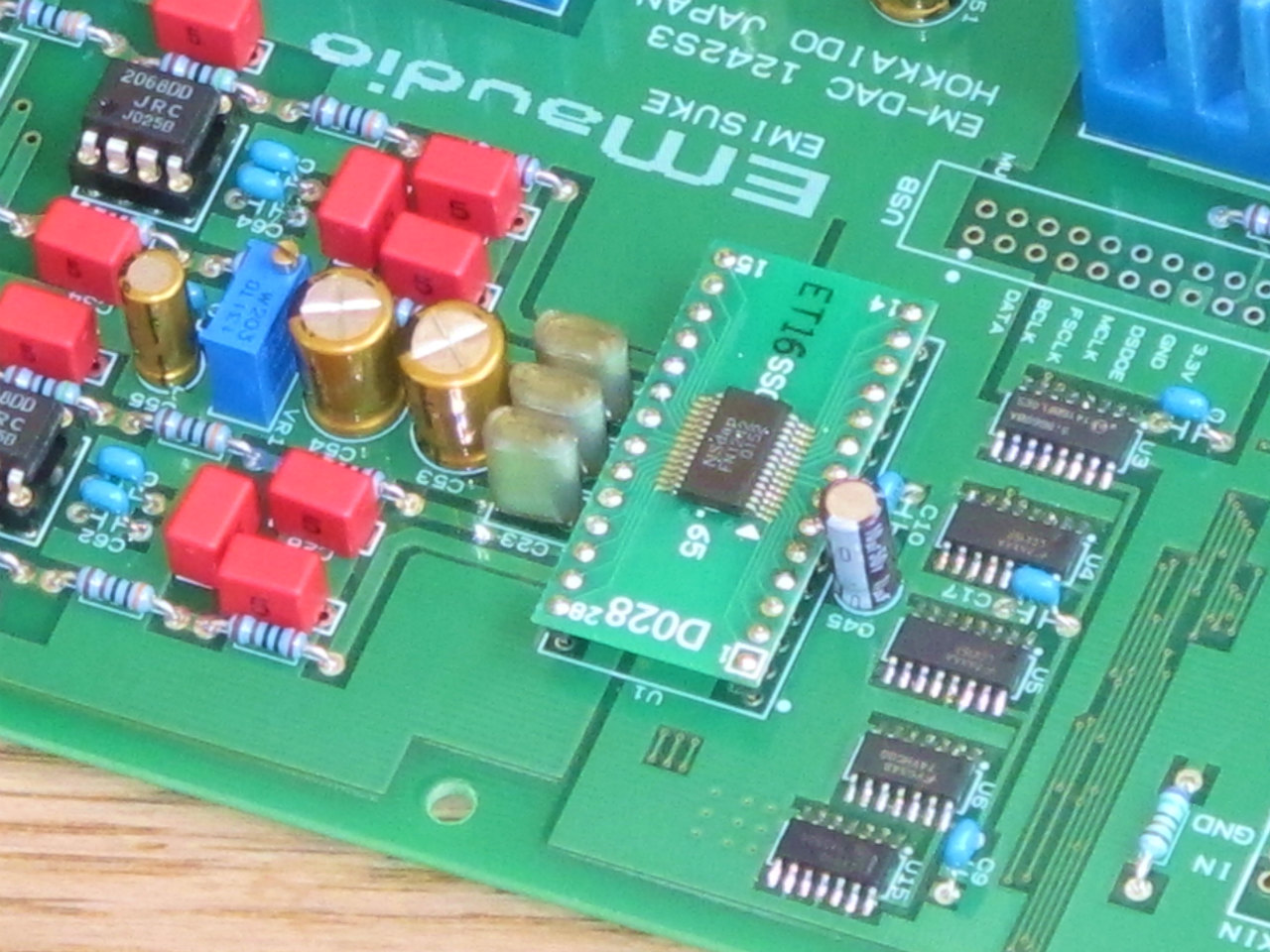

丂FN1242偼暿婎斅偲側偭偰偍傝傑偡丅

丂僺儞僿僢僞乕傪巊梡偟偰庢傝晅偗傑偡丅

丂

丂FN1242傪庢晅傞慜偵揹尮揹埑傪妋擣傪峴偄傑偡丅

丂FN1242幚憰抂巕偺

丂3.3V丄5V

丂婯掕揹埑亄亅俆亾埲撪偱偁傞偙偲丅

丂

倁俼侾挷惍

丂倁俼侾偼僶儔儞僗弌椡僆僼僙僢僩挷惍偱偡丅

丂慡晹昳庢晅屻丄倁俼侾傪挷惍偟傑偡丅

丂倀侾俀乮俷俹傾儞僾乯侾斣抂巕偺揹埑傪侽倁偵挷惍偟傑偡丅

丂倀侾俀亅俈斣丄倀侾俁亅侾斣丄倀侾俁亅俈斣抂巕偑侽倁偵側偭偰偄傞帠傪妋擣偟傑偡丅

丂俷俹傾儞僾偺僶儔僣僉偱姰慡侽倁偵偼側傜側偄応崌偑偁傝傑偡丄侽丏侽侾倁乮10倣倁乯埲壓側傜栤戣偁傝傑偣傫丅

丂

巊梡俷俹傾儞僾

丂俷俹傾儞僾偼丄僎僀儞侽偱埨掕摦嶌偡傞埵憡曗彏撪憻昳傪巊梡婅偄傑偡丅

丂僆乕僨傿僆梡側傜傎傏戝忎晇偱偡丅

丂晹昳庢傝晅偗曽岦側偳幨恀晄慛柧売強偼丄倂倕倐傛傝僨乕僞乕僔乕僩摍傪擖庤偟偰妋擣婅偄傑偡丅

丂擖弌椡偺僐僱僋僞乕偼俰俽俿偺倁俫傑偨偼倃俫僐僱僋僞乕偑揔崌偟傑偡丅

丂

廳梫晹昳偼丄攝晅悢偟偐庤帩偪桳傝傑偣傫丄傛偭偰僴儞僟晅偗幐攕帪偺擖庤偼丄偛帺恎偱庤攝婅偄傑偡丅

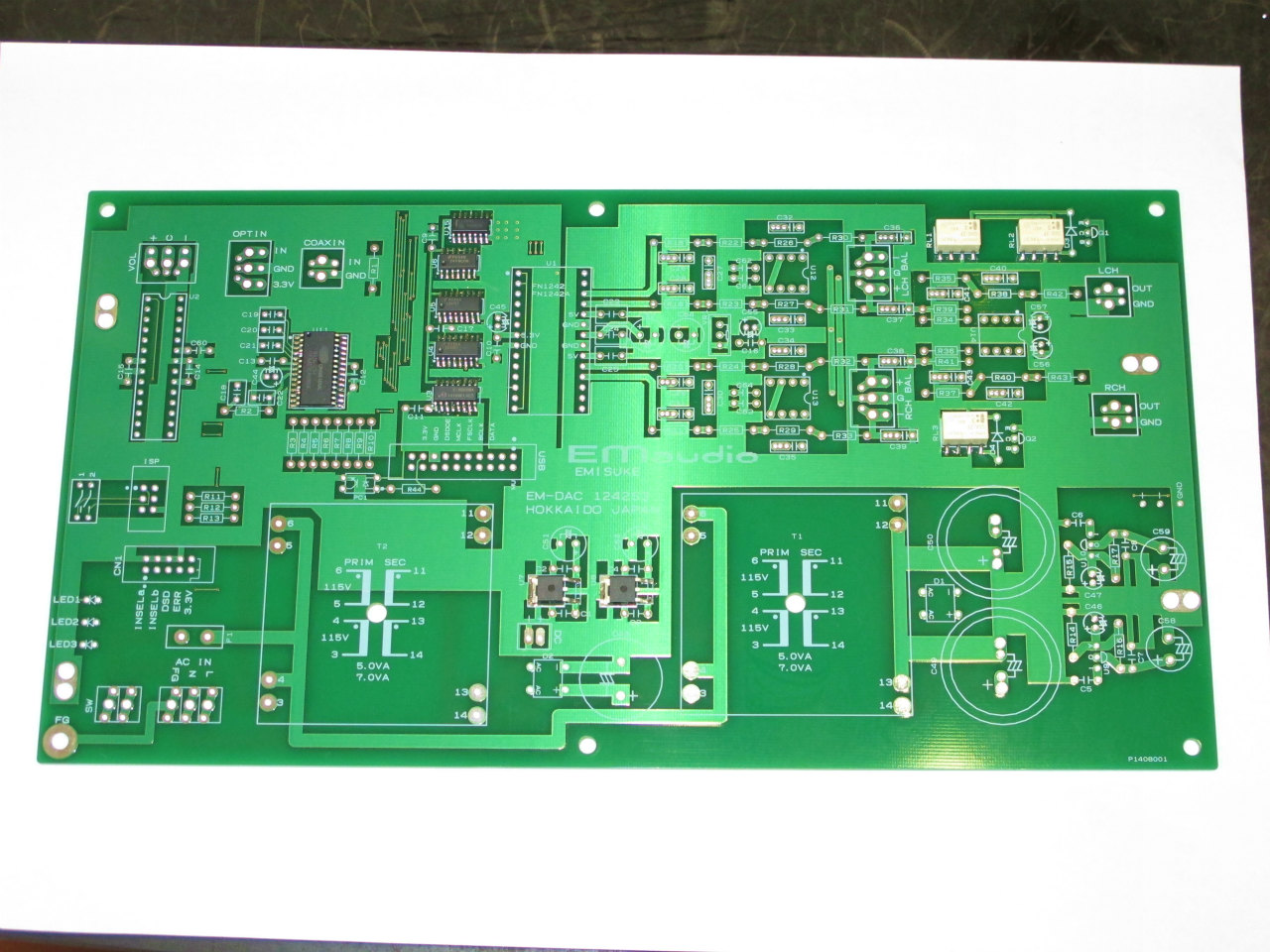

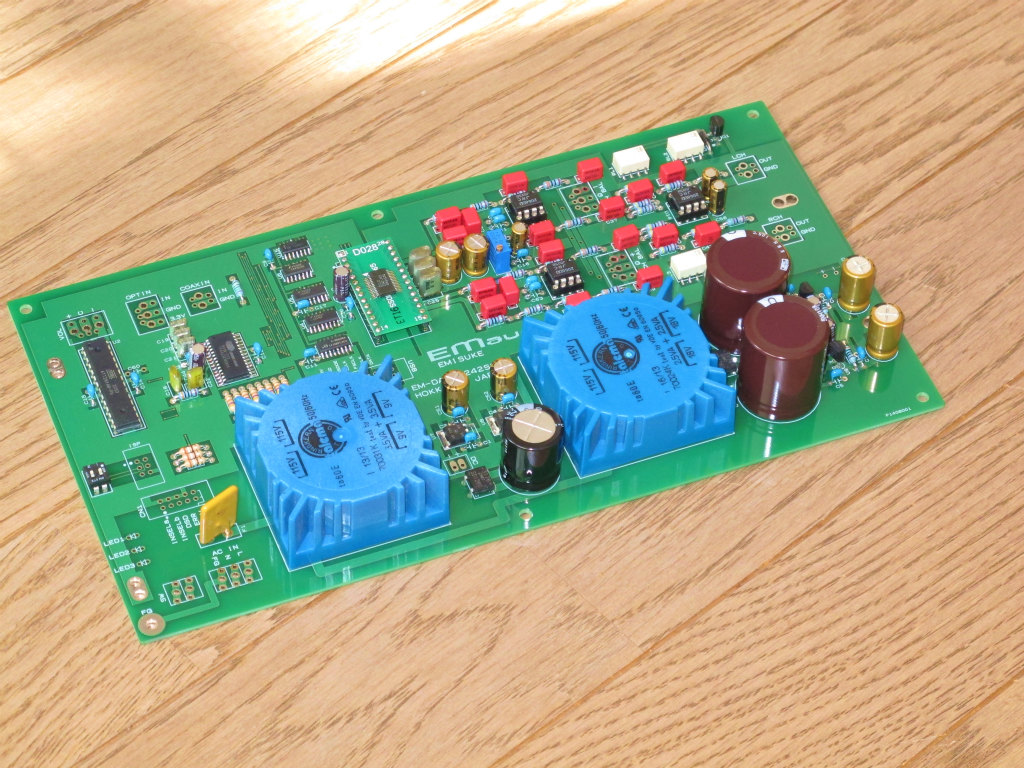

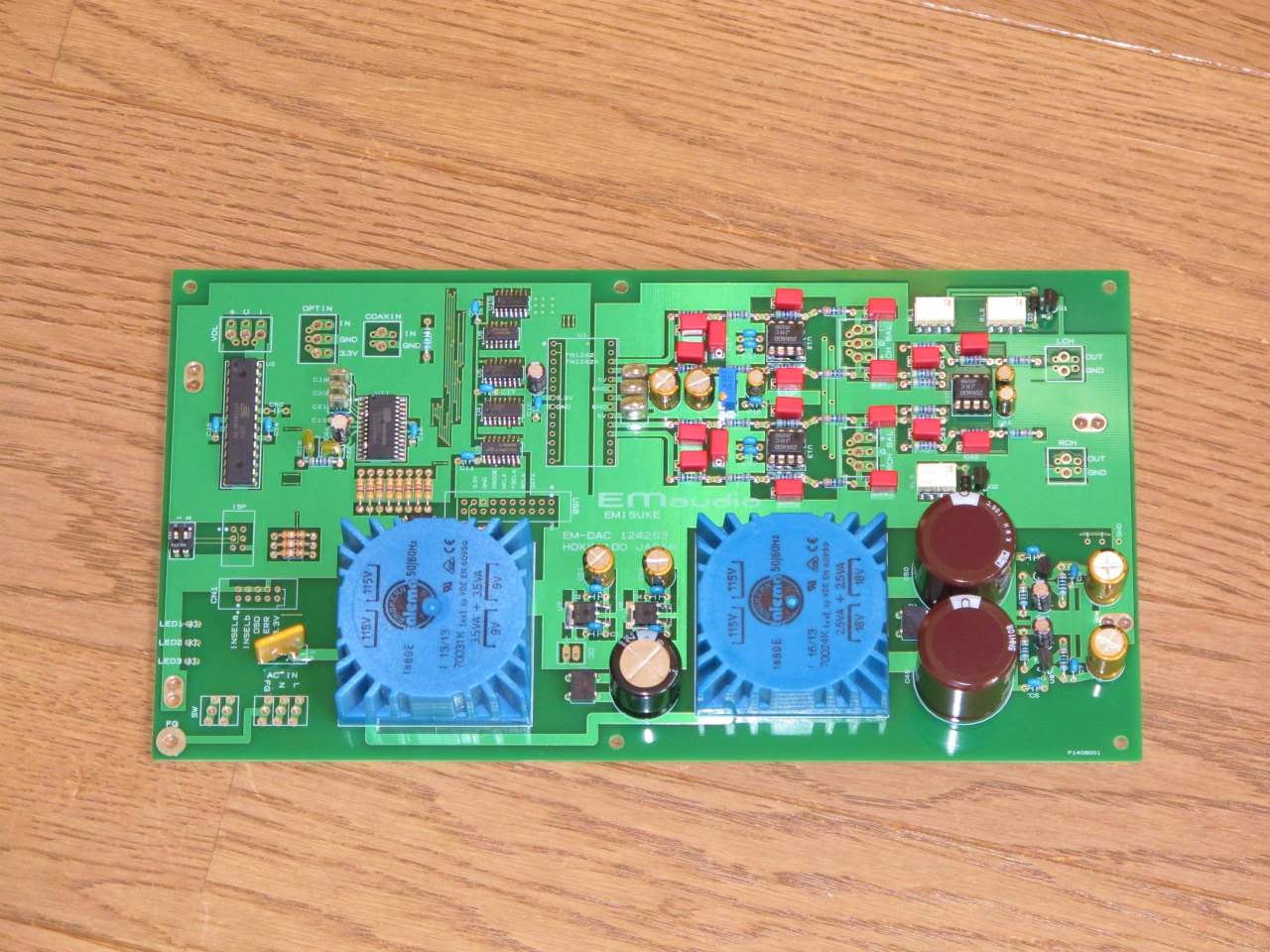

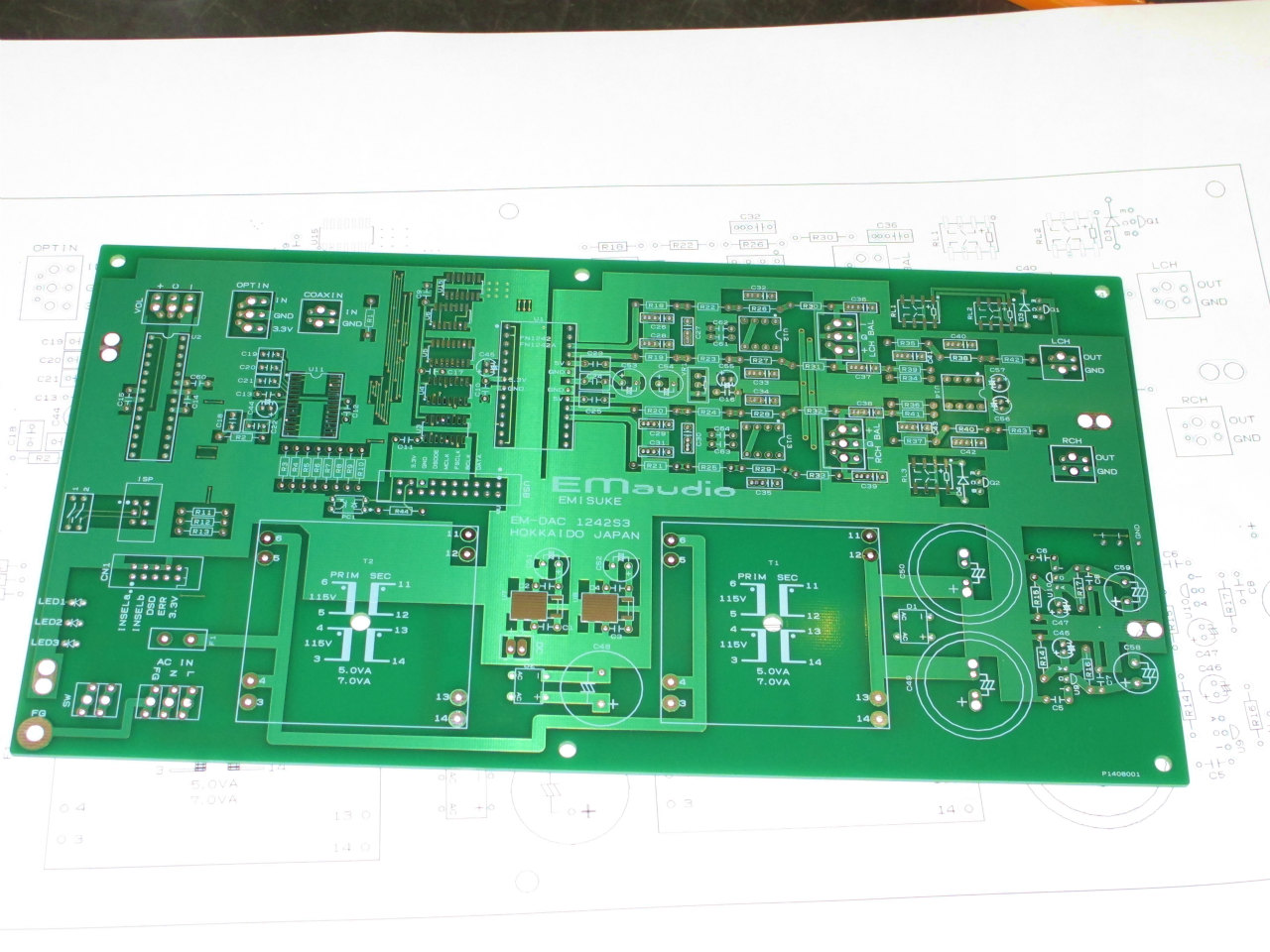

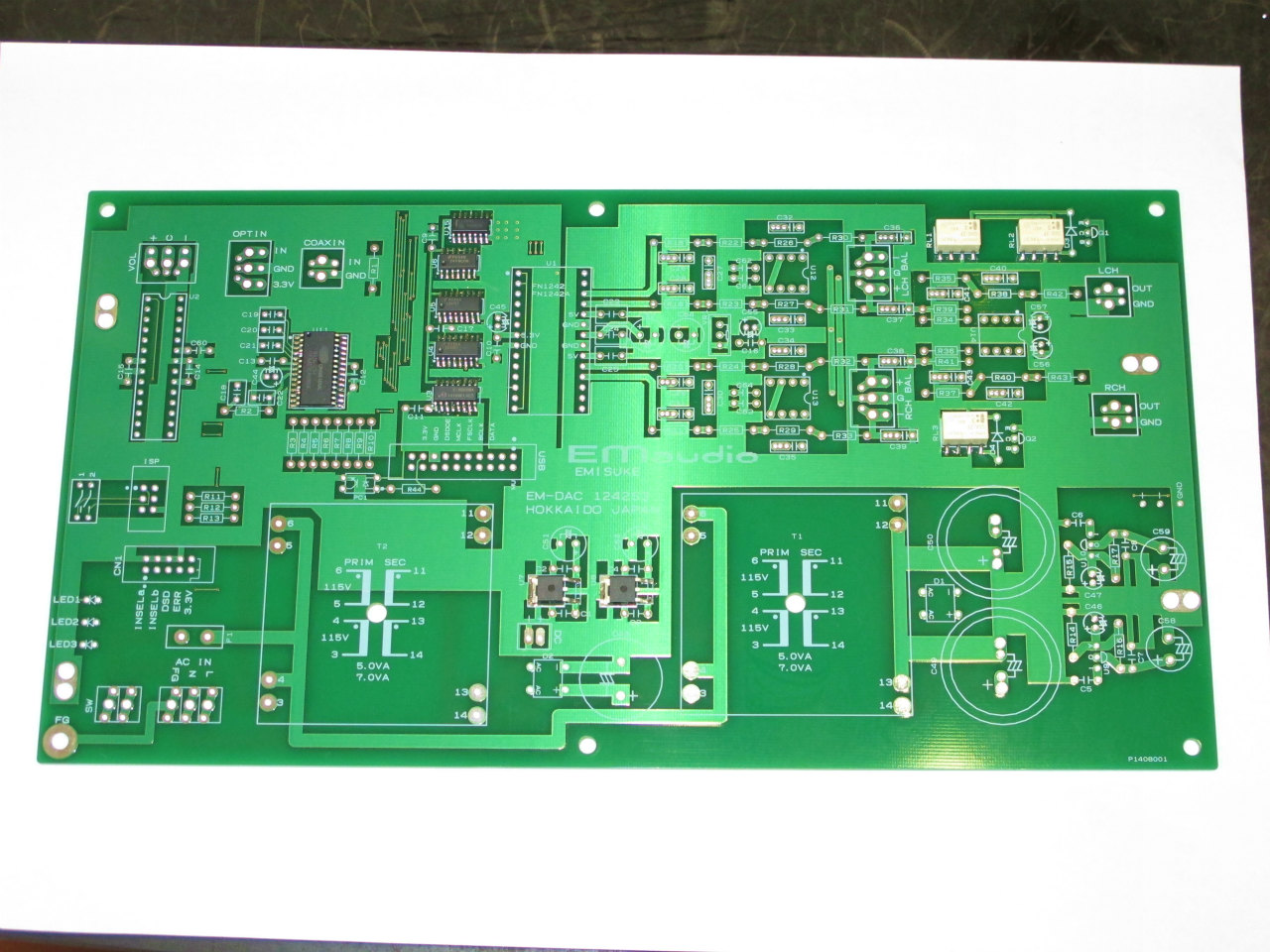

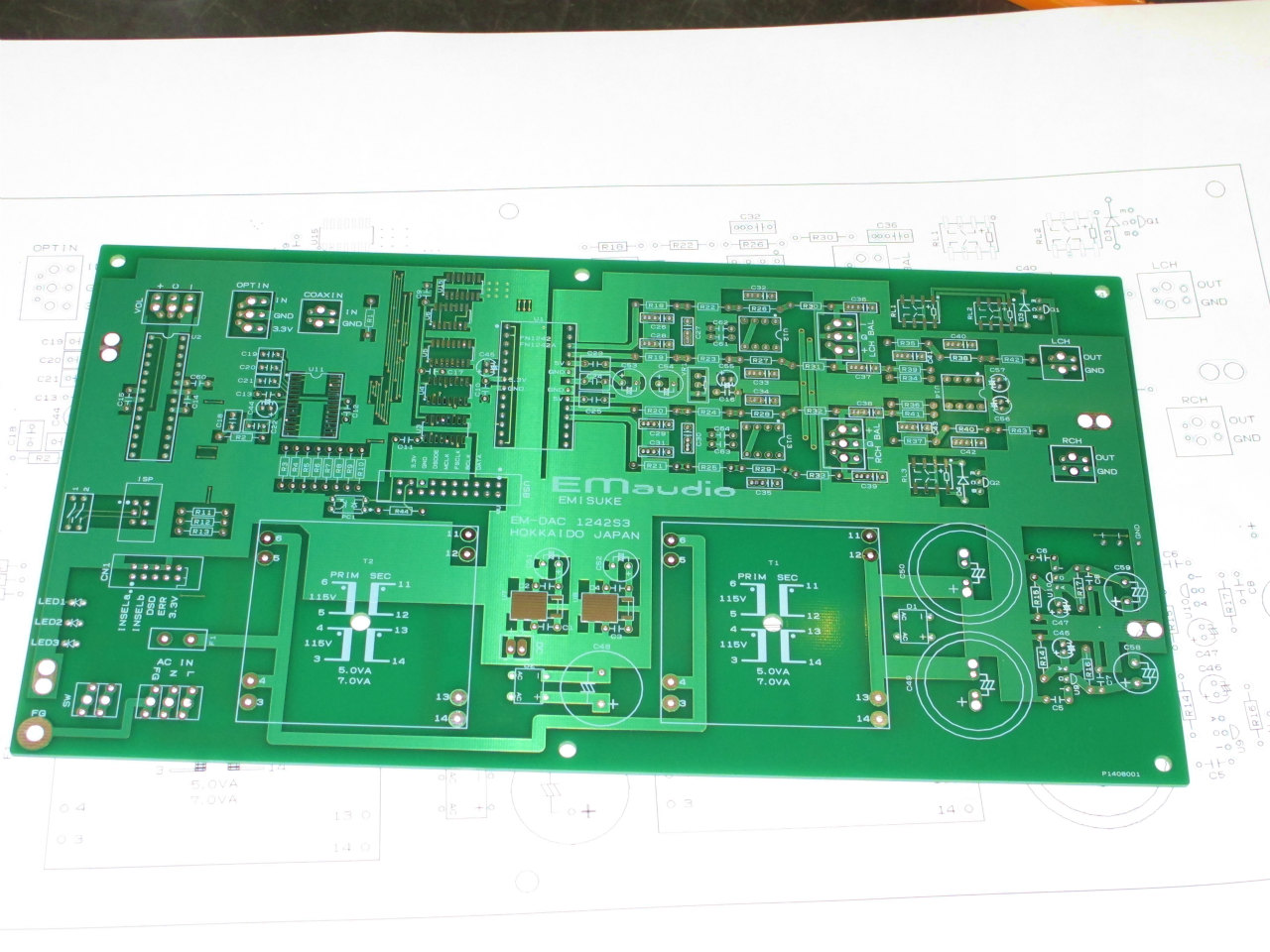

丂嶲峫幨恀

丂

丂婎斅僒僀僘偼丄僞僇僠揹婡 AWA15亅8亅26SS 偵擖傞僒僀僘偲偟偰偄傑偡丅

丂

丂嶲峫忣曬

丂丒杮婡偼丄傾儞僶儔儞僗弌椡偑斀揮弌椡偲側偭偰偄傑偡丅

丂丂惓憡弌椡偵偡傞応崌丄俛俙俴弌椡偲弌椡俷俹傾儞僾擖椡娫偱攝慄曄峏夵憿偱懳墳弌棃傑偡丅

丂丒俢俙弌椡俴俹俥掕悢偼丄俥俶侾俀係俀偺僨乕僞乕僔乕僩傪嶲峫偵寛傔偰傑偡丅

丂丂崱傑偱偺崅掞峈丄掅梕検愝寁偱側偔丄掅掞峈丄崅梕検掕悢偲側偭偰偄傑偡丅

丂丂傂偢傒棪偼庒姳埆偔側偭偰偄傑偡偑俥俶侾俀係俀偺僨僕僞儖僼傿儖僞乕曗姰偺摿挜偑弌偰偄傑偡丅

丂丂俥俶侾俀係俀俙僨乕僞乕僔乕僩傪嶲峫偵掕悢曄峏偟偰傕椙偄偐傕偟傟傑偣傫丅

丂

丂