参考結線図

掲載している写真では、配布品以外の部品が実装されている所があります。

添付部品は、写真と同等性能な他品の場合があります。

添付部品は、部品表を確認願います。

Ver1.0配布基板にバグがあります。 Ver1.1基板にはバグはありません。

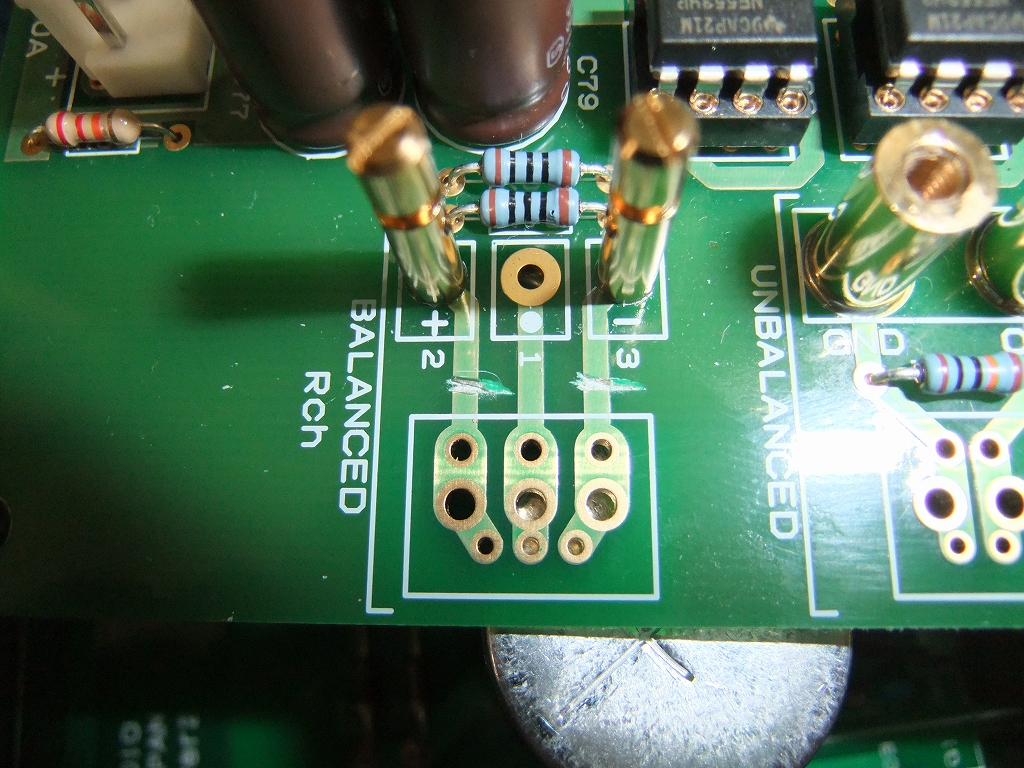

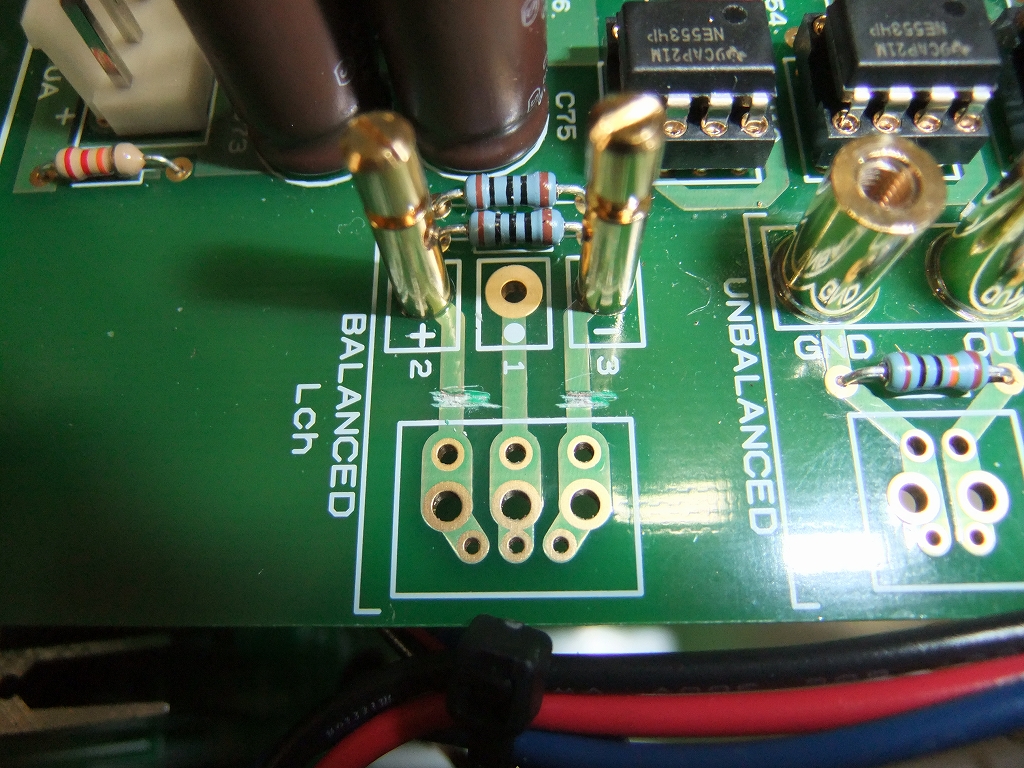

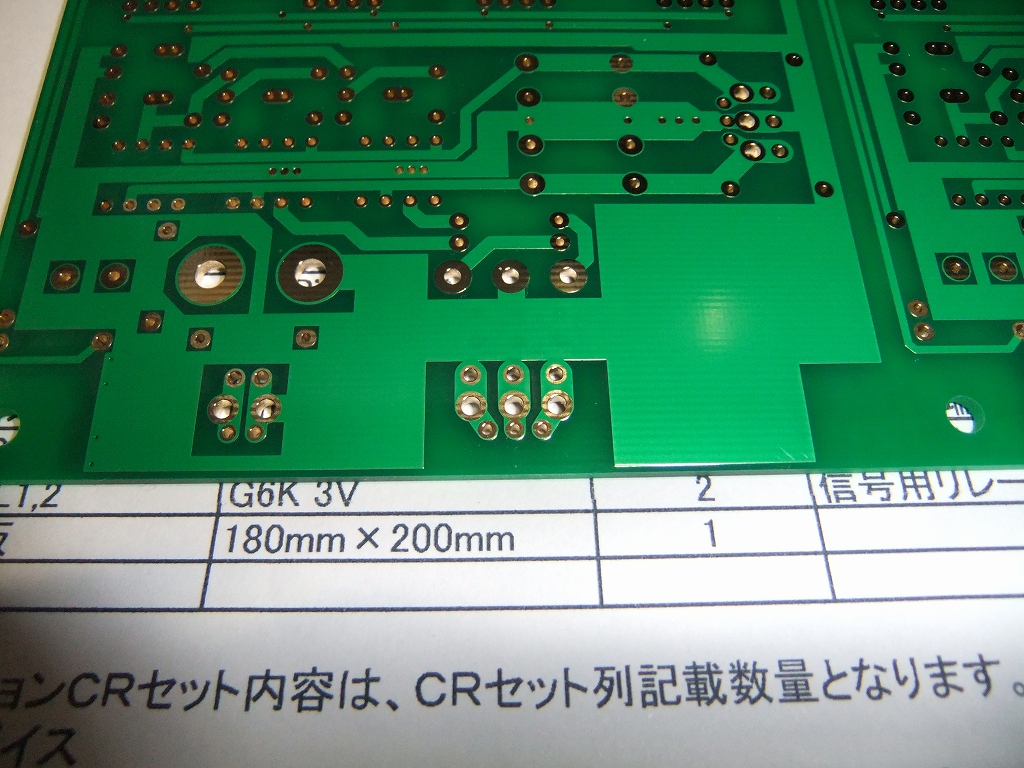

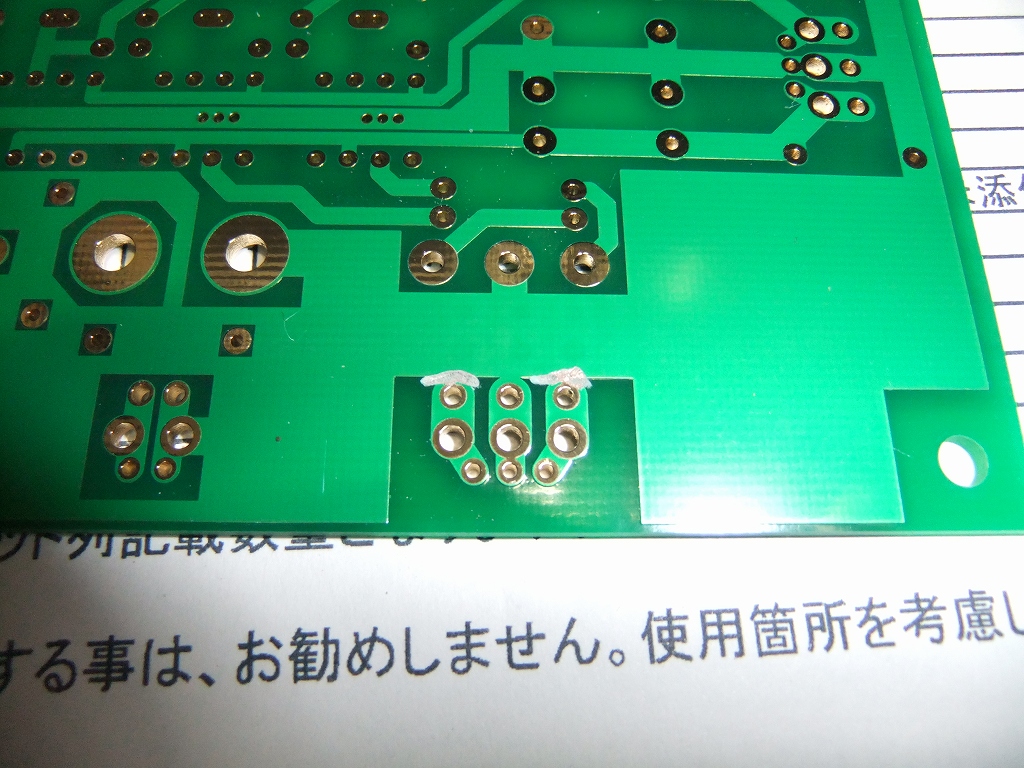

パターンカット4ヶ所です。

バランス出力端子がGNDとショートしています。

改造後バランス出力端子

改造後バランス出力端子写真上と写真下の端子を切り離します。

写真下の端子は使用できなくなります。上のみ使用可能です。

下端子部でGNDとショートしています。

基板裏面でカットすれば、上下両方の端子が使用可能です。

改造前

改造前

改造後

改造後バランス出力を使用しない場合は、基板改造不要です。

代わりにR76、R77、R79、R80の100Ω抵抗を実装しません。

本品は、回路図が理解できて自作ベテラン向けです。

当方は自分用で動作確認済みで、回路図通り組立てれば動作します。

よって中上級者向け配布とし、不動時は、ご自身の力で解決願います。

掲示板等で聞くのも良いかと思います。(製作上の質問は、掲示板でお願いします。)

部品数は、200個以上です。

製作難易度は・・・高・・・です。

基板及び回路図記載の電源を接続願います。アナログ部の電源は、+−12〜18Vにして下さい。

オプションの電源を使用するか、別途用意してください。

デジタル回路用電源は、別途+5V(1A以上)品を用意する必要があります。

スイッチング電源が簡単だと思います。 (LCD、VFD表示の場合、2A品)

GNDアイソレータ搭載でノイズ耐性が高いですので問題なく使用できます。

表示選択

組立て前に、LED表示又はLCD表示を選択します。

POW LEDのみ単独使用可能です。

その他LED端子は、LCD接続時は使用できません。(接続できません)

同じく、LED使用時は、LCDは使用できません。(接続できません)

SW、LED説明

IN SW 入力選択。OFF(オープン)でIN1、ON(ショート)でIN2。

FIL SW デジタルフィルター特性切替。OFF(オープン)でSHORT、ON(ショート)でSHARP。

48K SW , 96K SW 出力FS選択

OFF OFF BYPAS

ON OFF 48K

OFF ON 96K

ON ON 192K

両方共OFFにした場合、SRC(サンプリングレートコンバーター)を迂回し、入力信号が直接D/Aへ入力されます。

POW LED 電源ランプです。

ERR LED 入力信号異常、同期はずれで点灯します。

IN1 LED IN1入力選択時に点灯

IN2 LED IN2入力選択時に点灯

SHORT デジタルフィルタ特性SHORT選択時に点灯

SHARP デジタルフィルタ特性SHARP選択時に点灯

192K 出力FS 192K選択時に点灯

96K 出力FS 96K選択時に点灯

48K 出力FS 48K選択時に点灯

BYPASモード時は、出力FS LEDがすべて消灯します。

端子

LCD1,LCD2 LCD使用時にLCDモジュールを接続。

どちらか片方のみ使用します。

メーカーによりLCDの端子配列が違う為、接続を簡単にする為、端子配列が違う端子です。

使用品に合わせ端子選択願います。端子配列は回路図参照の事。

ISP CPU書込み用端子(通常時未使用)

CN SW/LEDの外部引出し端子

IN1、IN2 デジタルオーディオ信号入力

+5V IN端子横は、OPTモジュール用電源出力

PU +5V LED端子横は、デジタル部電源入力+5V(1〜2A)

A+K- LCDバックライト用電源

OPT IN(光入力)

IN1、IN2は、標準部品を実装した場合、COAX(同軸)入力となります。

OPT入力で使用する場合は、IN端子に接続されている75Ω抵抗は実装しません。

75Ω抵抗を実装するとエラーとなり受信できません。最悪TORXモジュールが壊れます。

回路図参照の事。

JP設定

CPU1 OFF設定にする事

CPU2 状態表示方法の選択

ON:LCD使用

OFF:LED使用

POL CPLD設定

ON設定にする事

OFFの場合音が出ません。

SM CS8416は、入力信号がERR状態の場合、D/Aへ不確定信号を出力してしまいノイズとなり聞こえる場合があります。

CSS8316がERR状態で、D/Aへの出力信号をON/OFFさせる回路を追加しました。

ON:信号制御しない。(再生信号頭切れなど発生時の対処) 最下段追加参照

OFF:ERR状態で信号OFF制御する。

CPU実装

AK4399は、CPU制御でデーター設定されて音が出ます。

よって、CPU不良、未実装では音が出ません。

CPU起動

CPUの起動に成功すると。

LEDモード

POW LED以外の全LEDが点灯します。

その後、SW状態にそったLED点灯となる。

LCDモード

起動すぐにEMISUKE AUDIOと表示されます。

その他注意点

CPLDの実装方向には十分注意願います。

どの方向にも刺さりますが正規方向以外では当然CPLD破損します。

部品取り付け方向など写真不鮮明箇所は、Webよりデーターシート等を入手して確認願います。

28P SSOP部は、サブ基板を使用する事も可能です。

指定サブ基板 ダイセン電子 D028基板

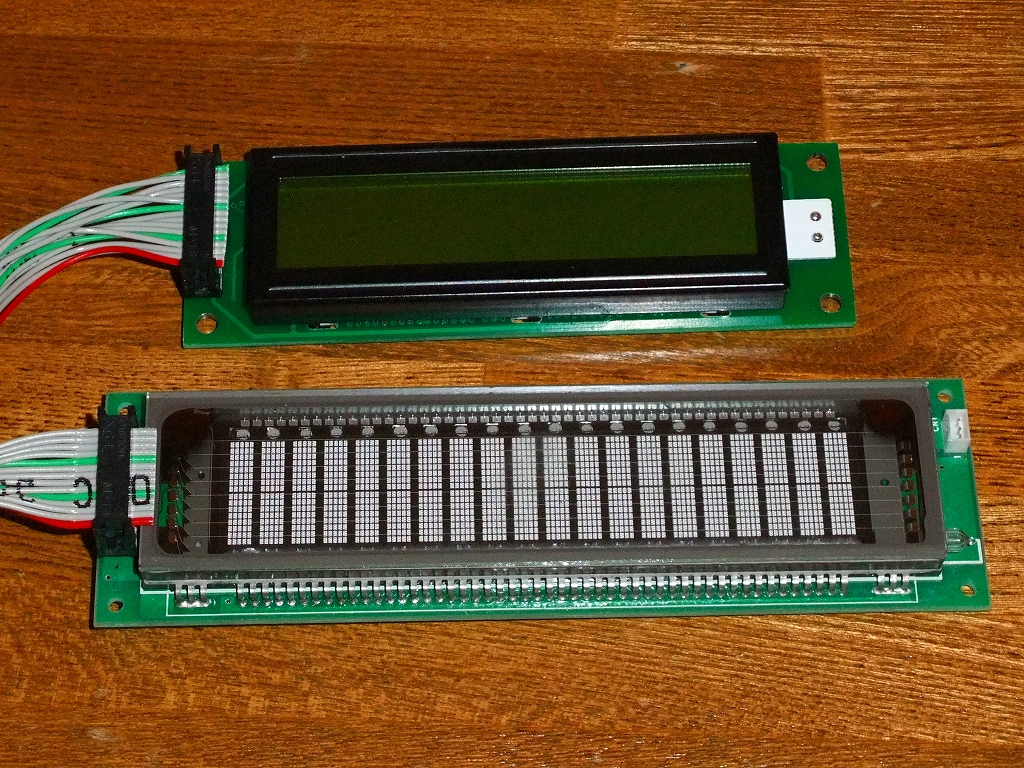

使用可能LCDは、20*2表示品です。

本文記載時点では、秋月で入手出来ません。

私は下記で入手しました。

http://www.aitendo.co.jp/ 型式 SC202A

LCD実装時は、接続端子配列に注意願います。

メーカーにより電源配列など違います。

回路図、データーシートで使用端子確認願います。

LCD互換品のVFDも使用可能です。HD44780コンパチブル M68モード

表示内容

1行 入力情報 入力チャンネル 入力状態:ERR異常/SYNC正常

2行 出力情報 デジタルフィルター 出力FS周波数

重要部品は、配付数しか手持ち有りません、よってハンダ付け失敗時の入手は、ご自身で手配願います。

特にAK4399

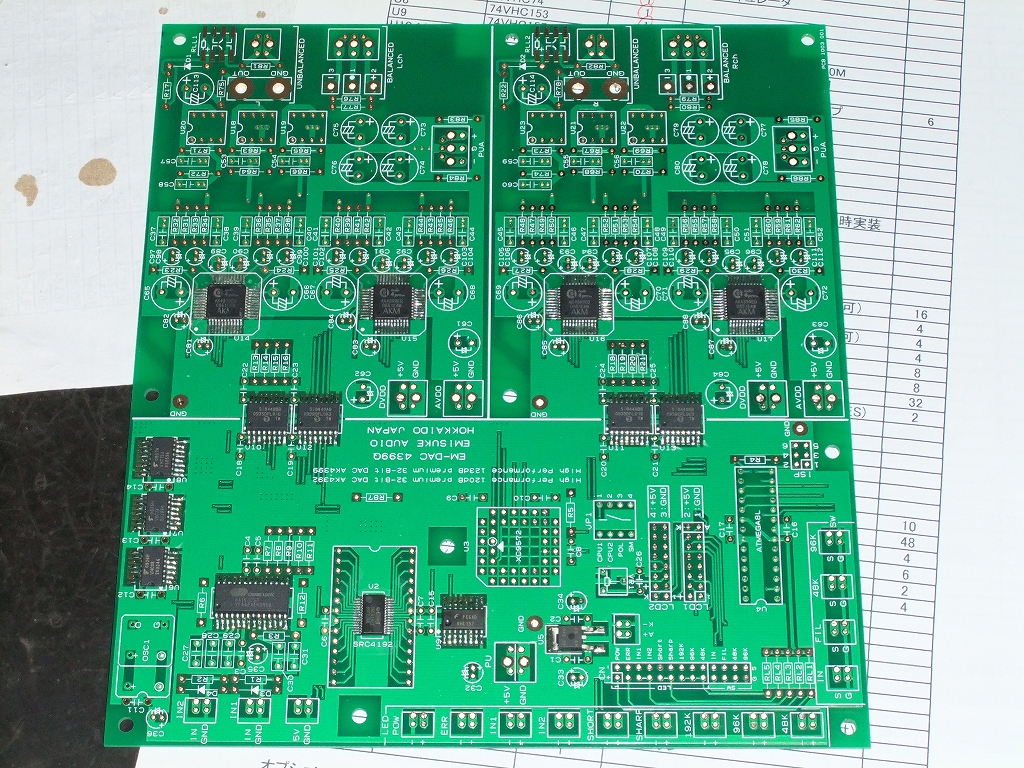

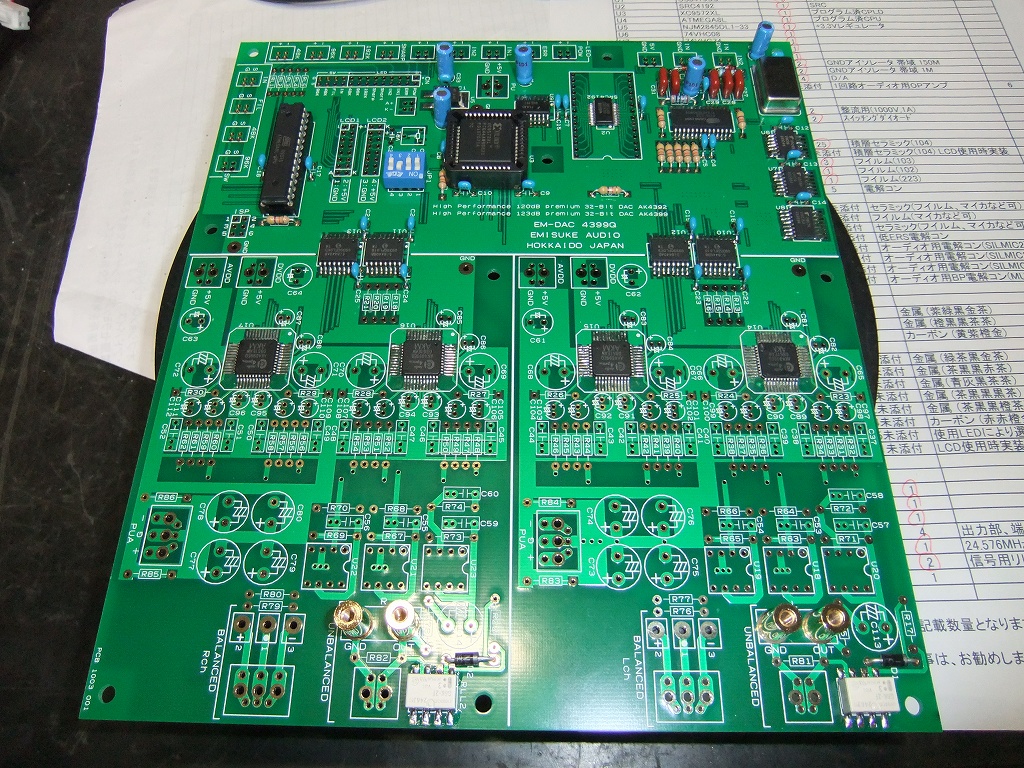

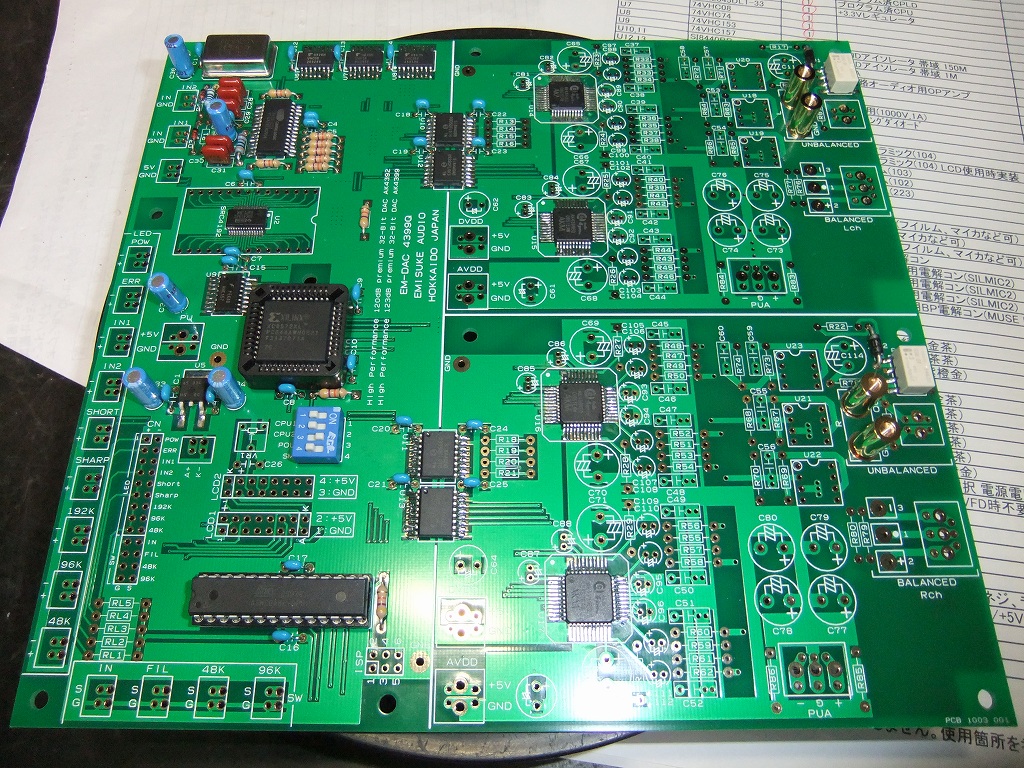

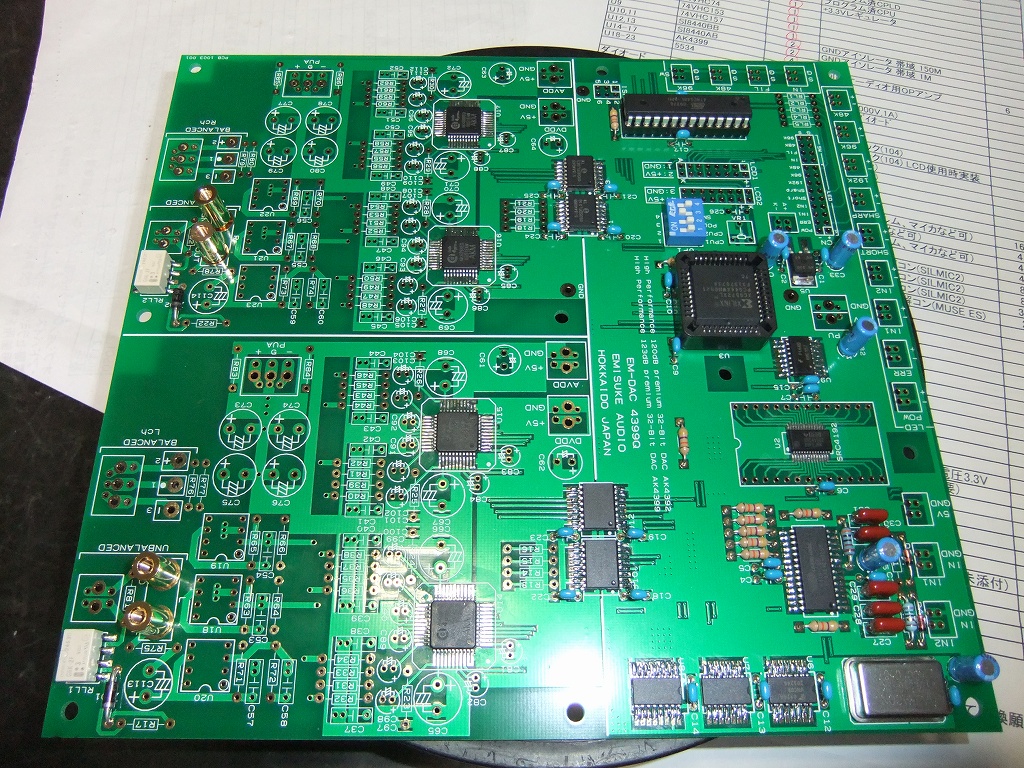

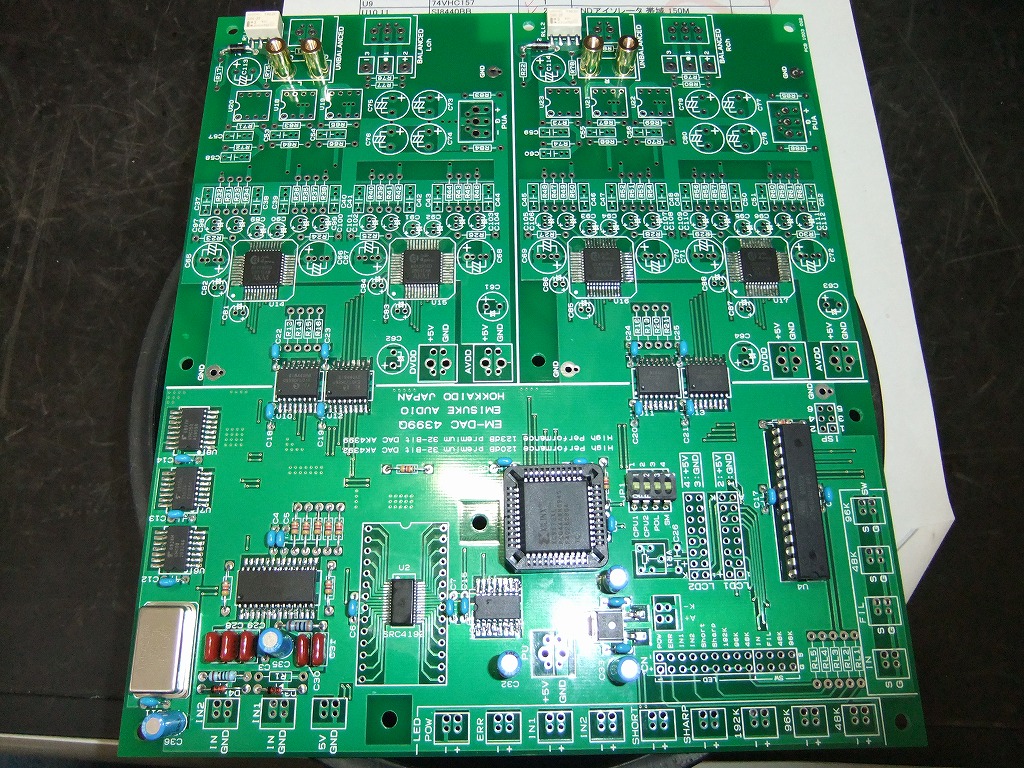

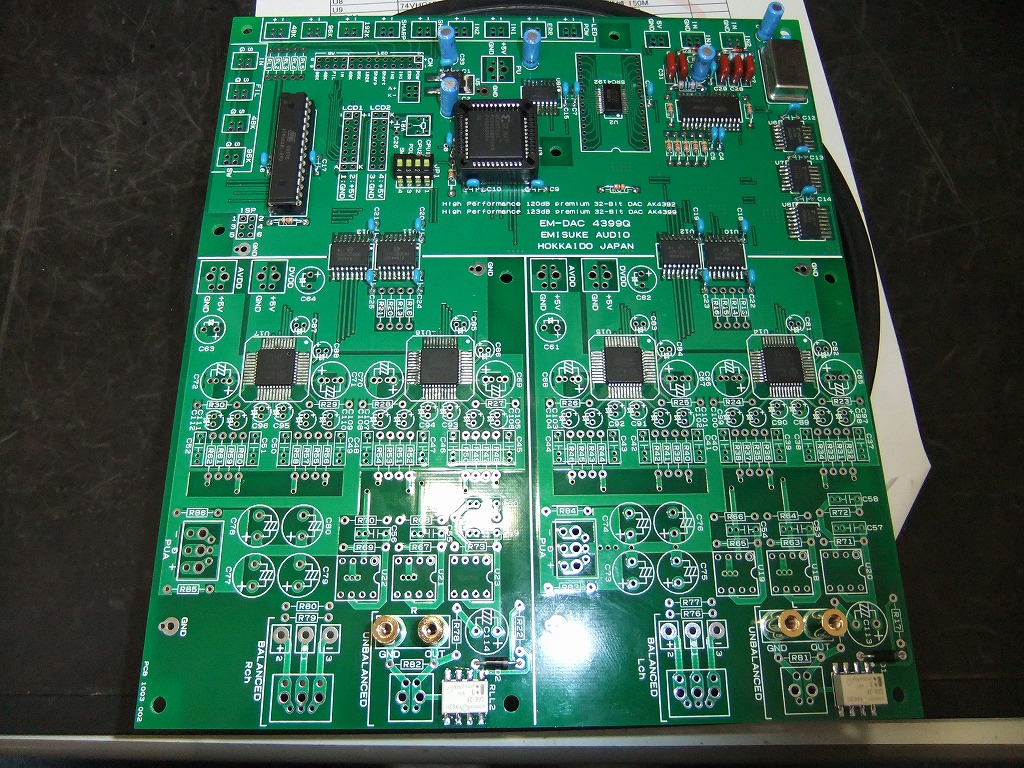

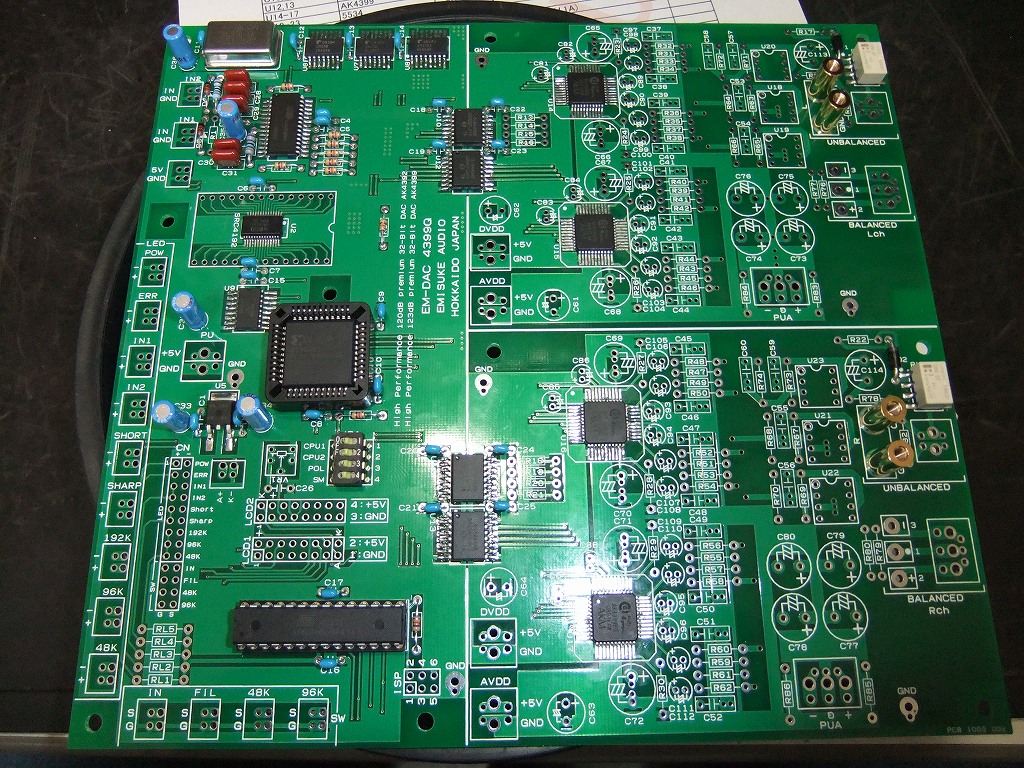

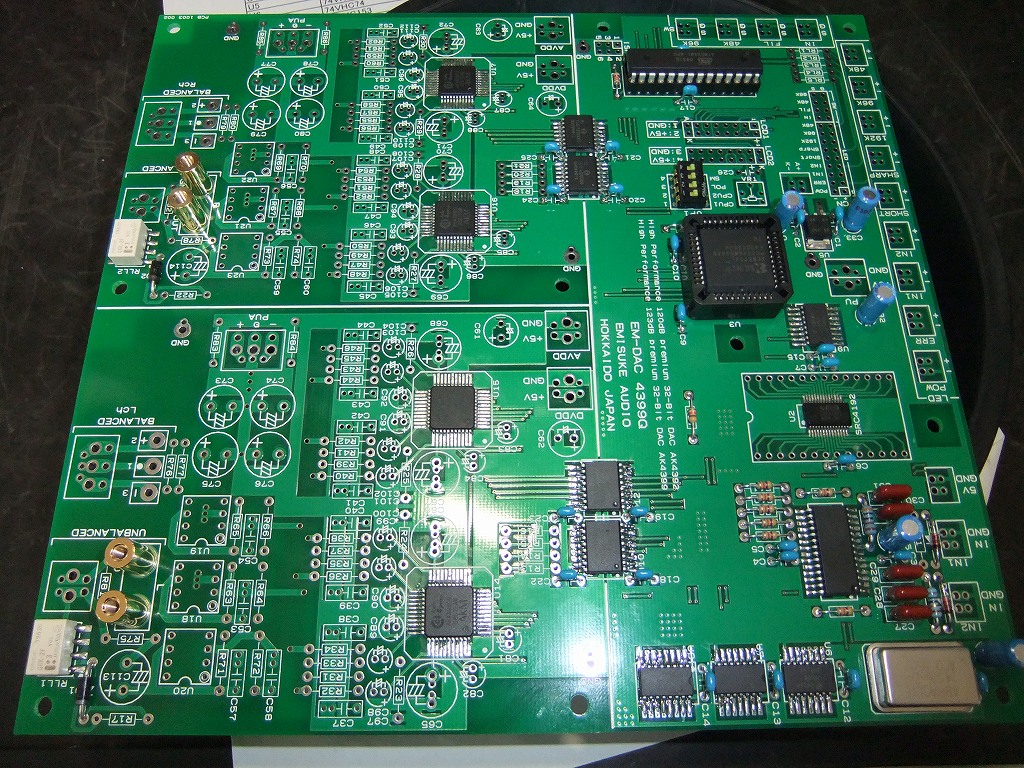

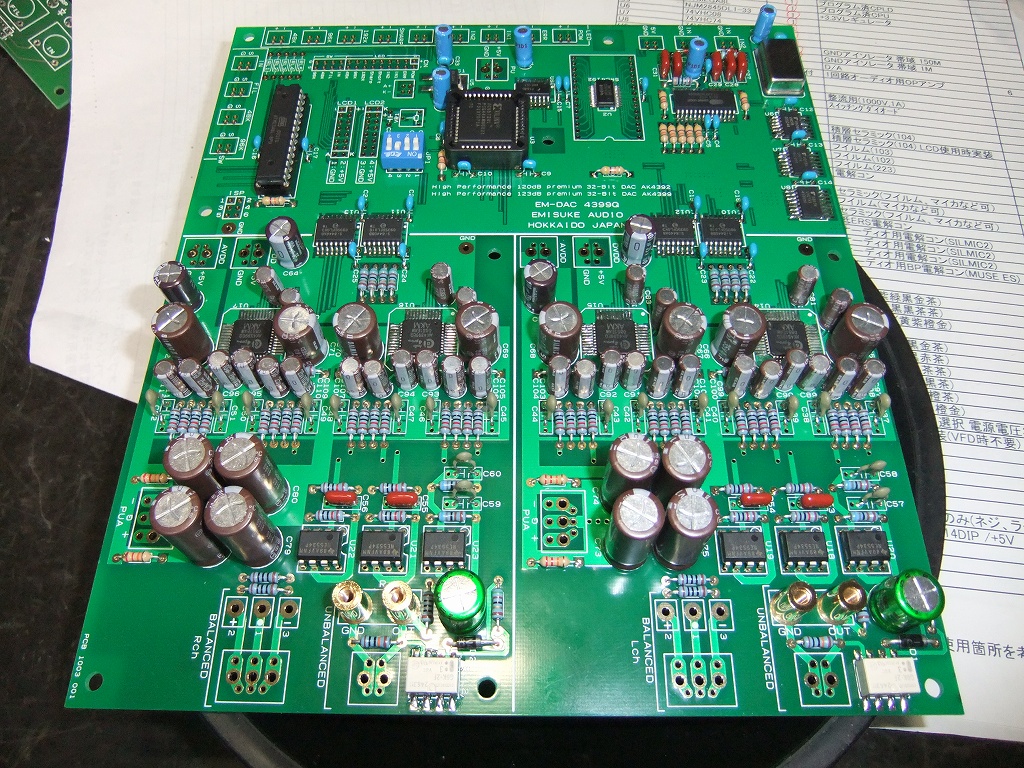

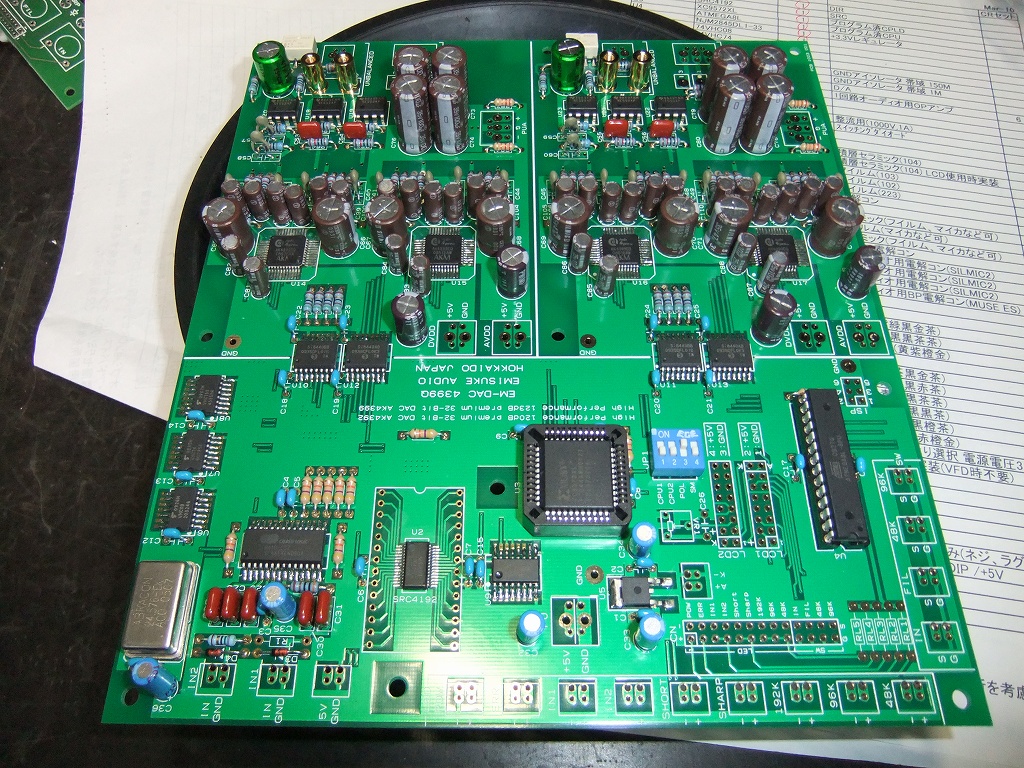

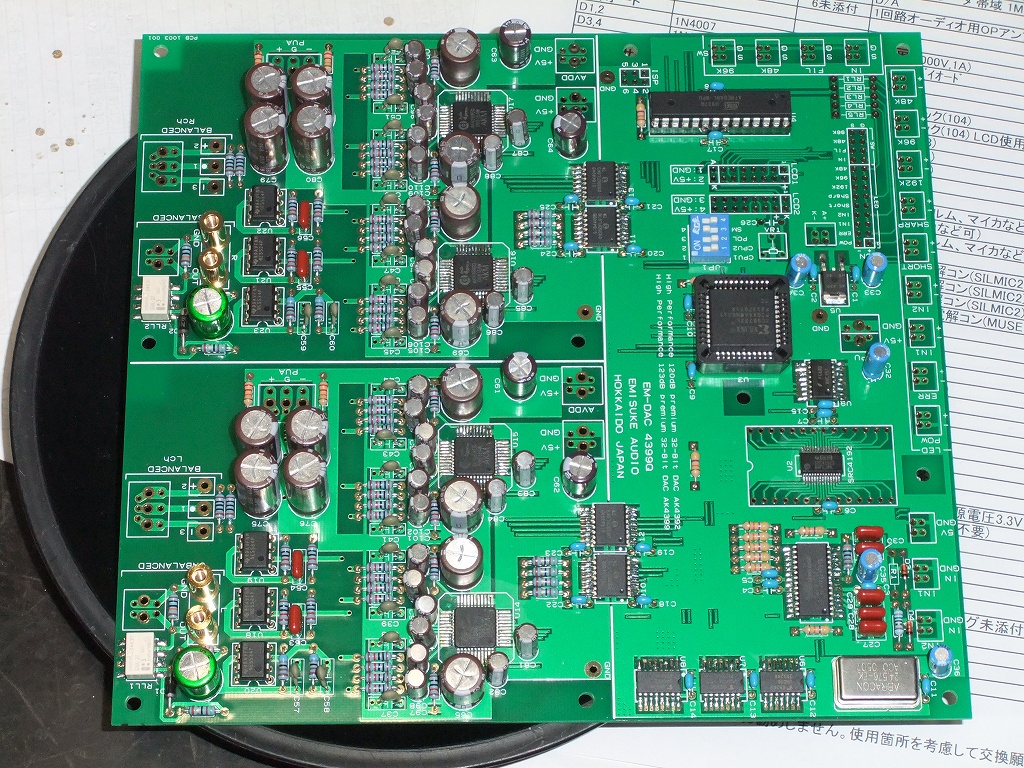

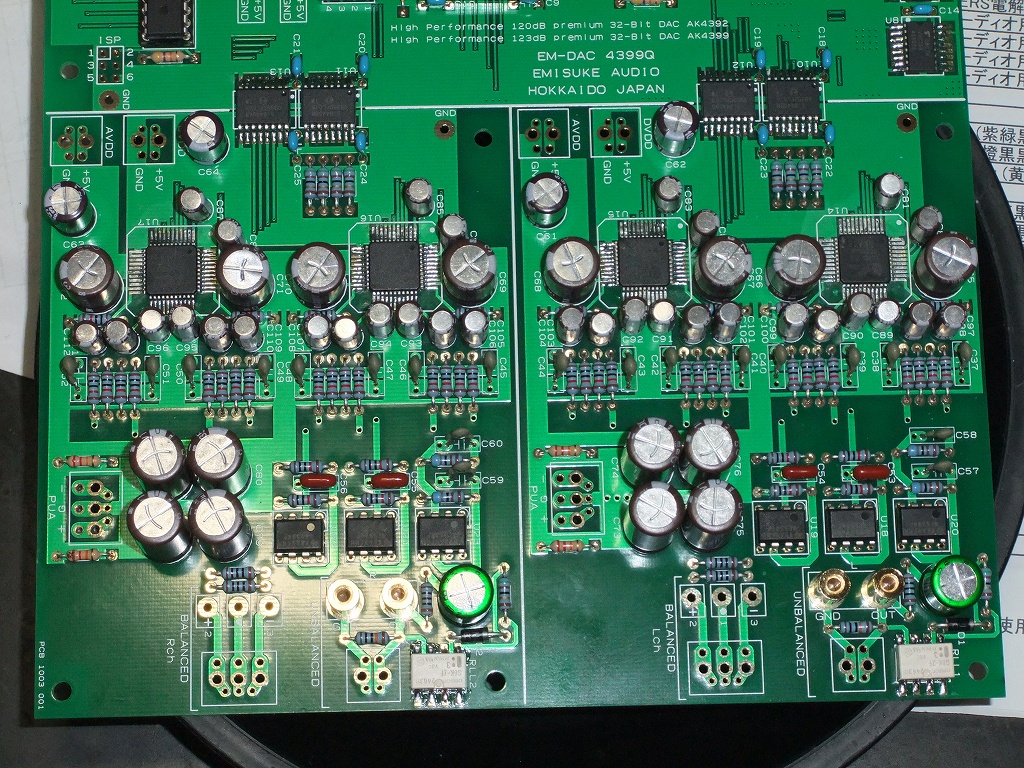

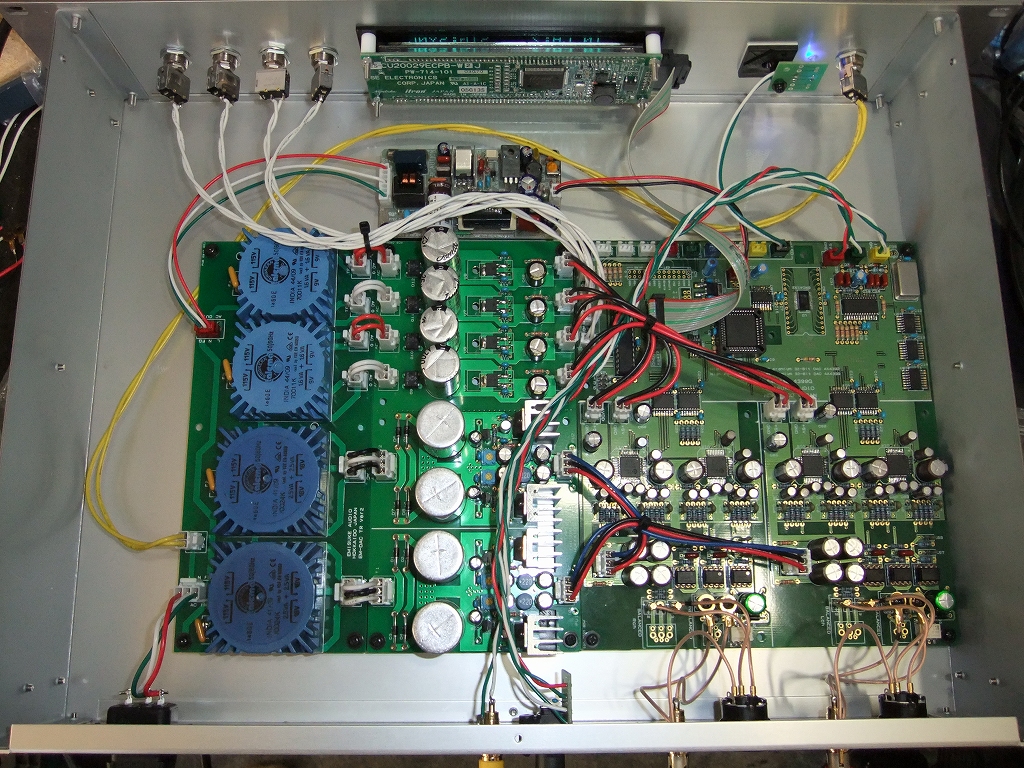

参考写真

・Ver1.0標準配布部品実装

・Ver1.1標準配布部品実装

・オプション CRセット実装状態

配布品以外の部品を実装している箇所があります。参考用

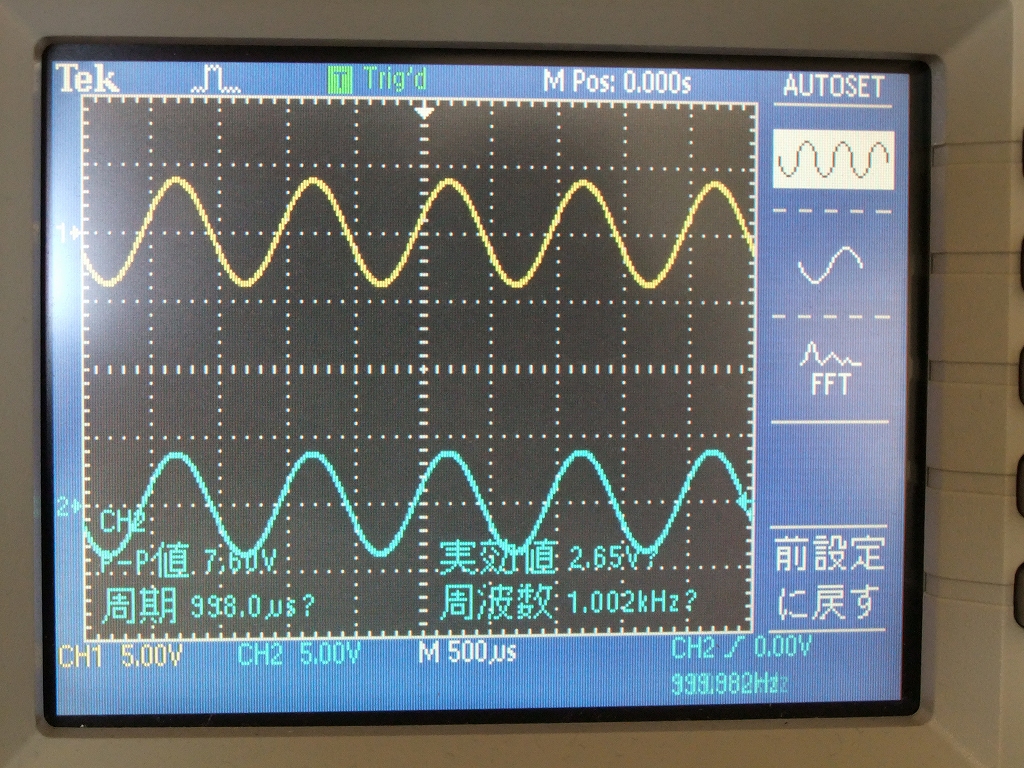

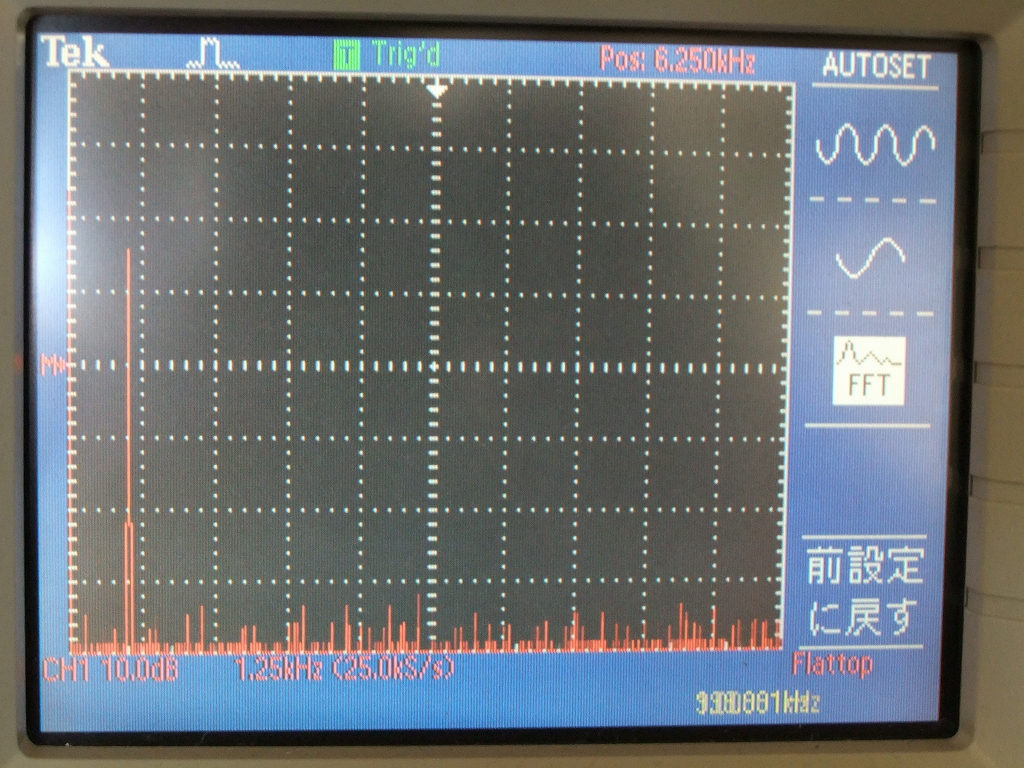

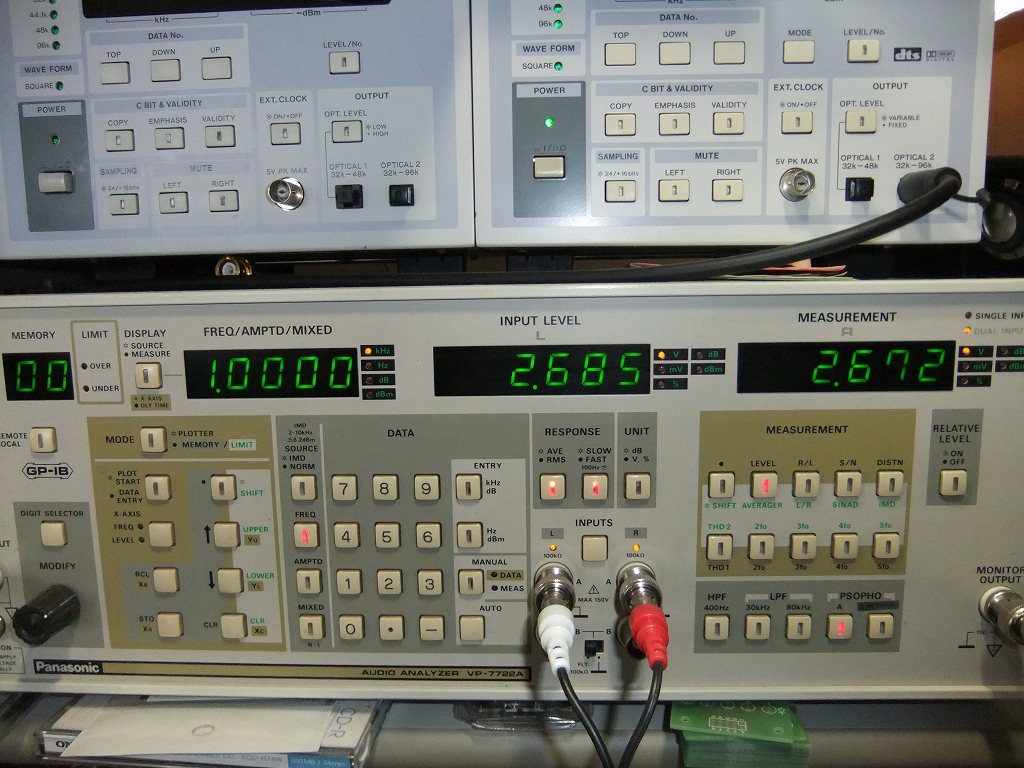

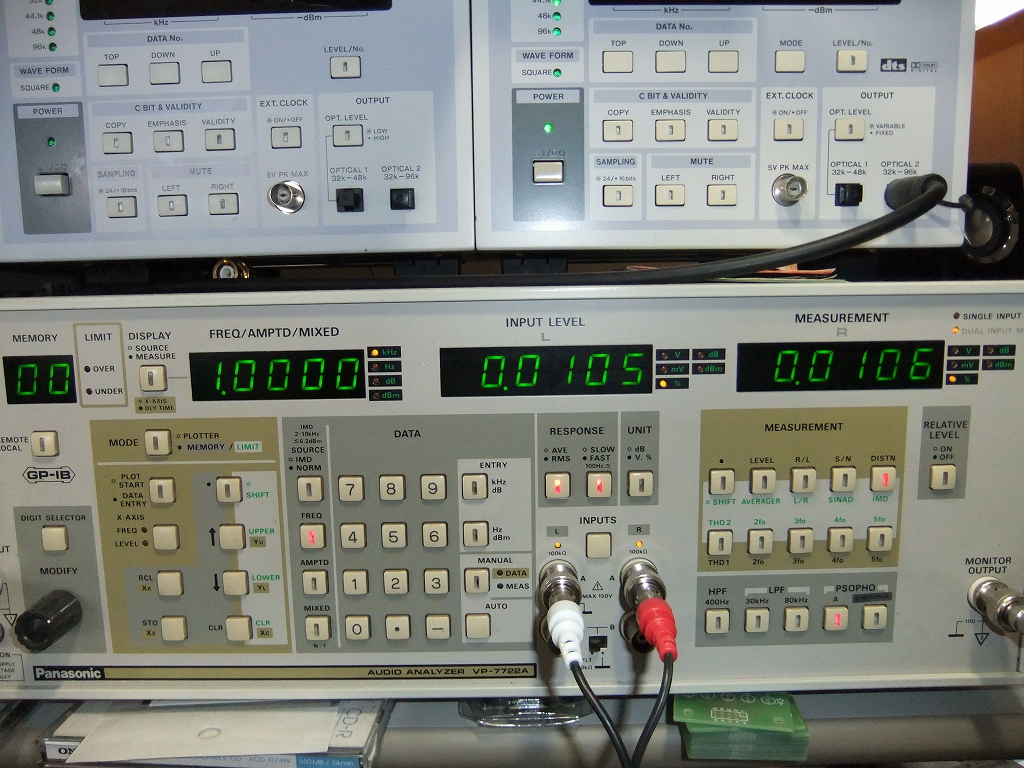

参考 試作動作確認品での特性

1KHz出力波形

1KHz出力波形 FFT波形

FFT波形 0dB出力電圧 約2.7V

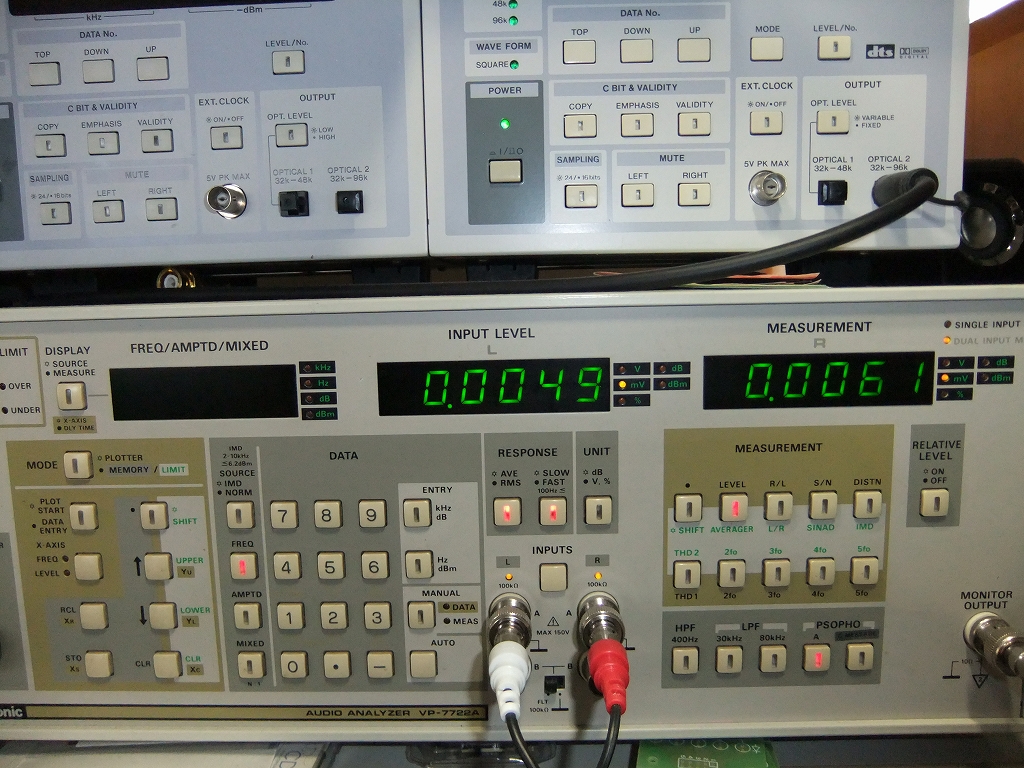

0dB出力電圧 約2.7V 無信号雑音電圧 約0.006mV

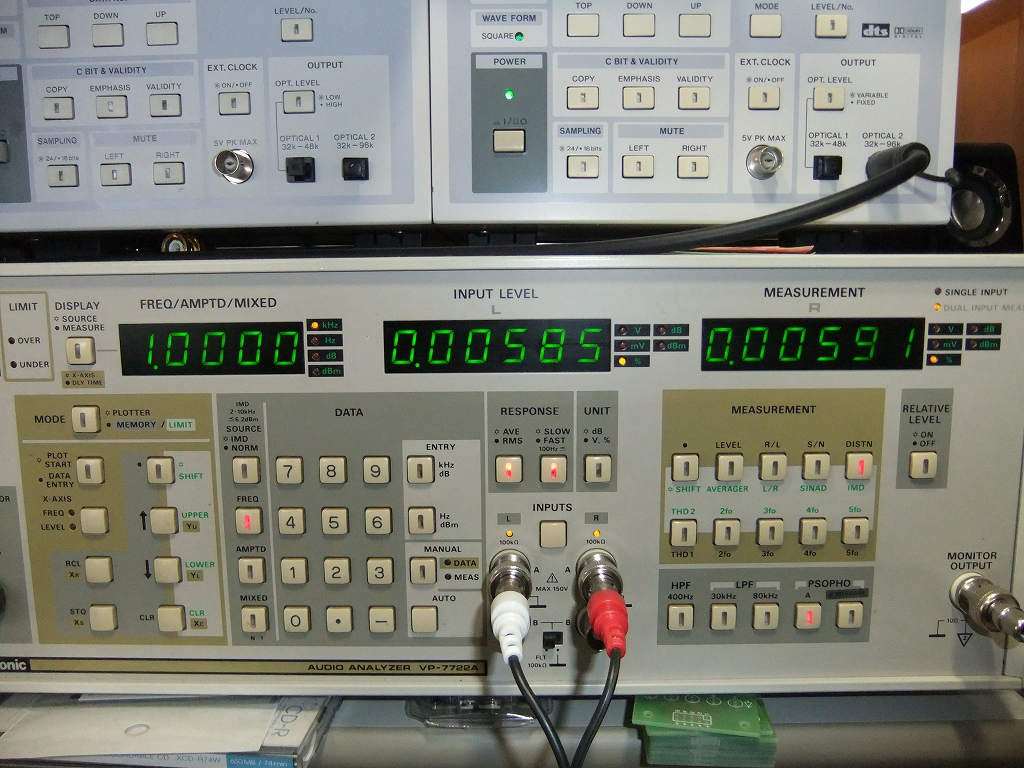

無信号雑音電圧 約0.006mV ひずみ率 FS192K 約0.006%

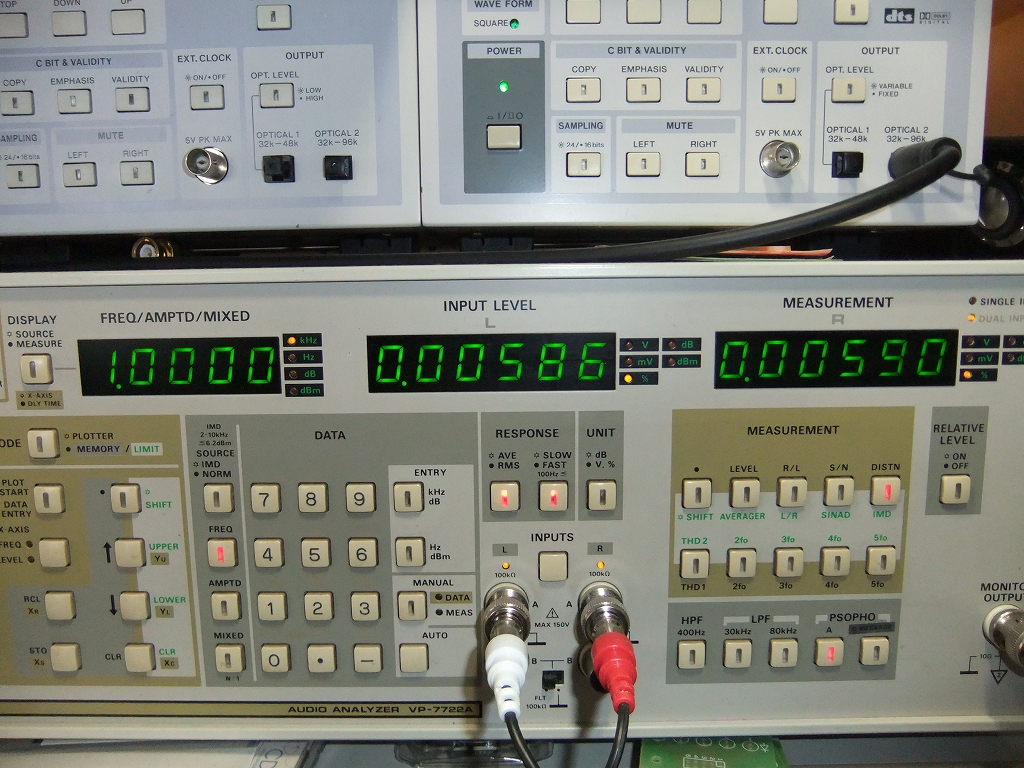

ひずみ率 FS192K 約0.006% ひずみ率 FS96K 約0.006%

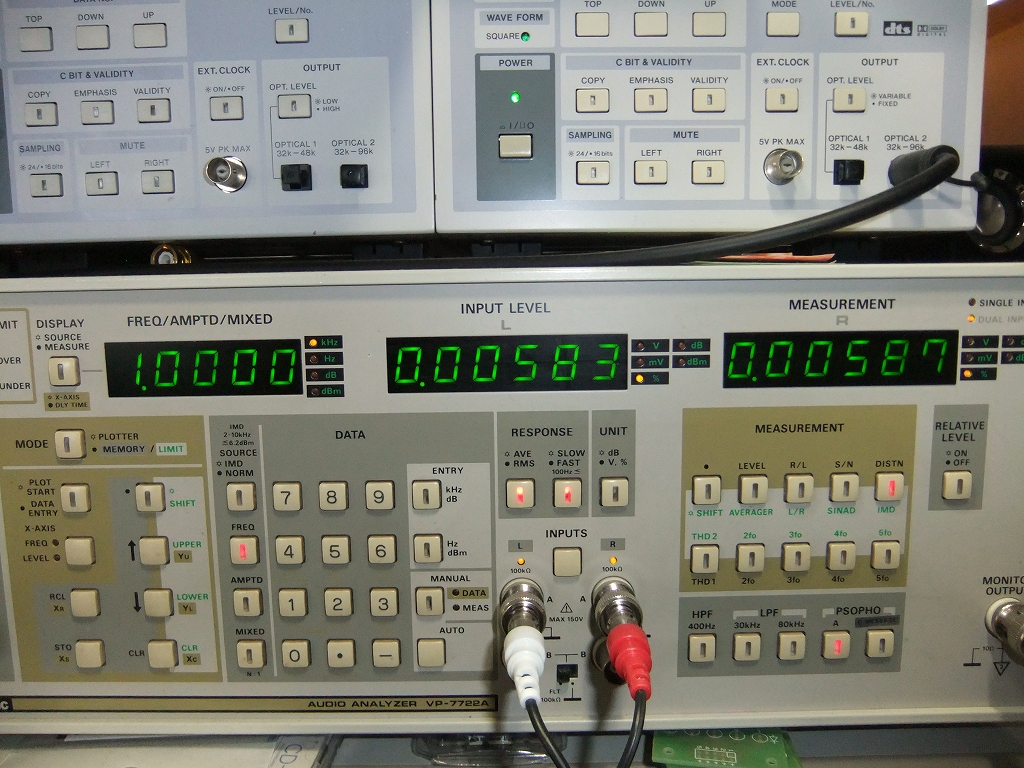

ひずみ率 FS96K 約0.006% ひずみ率 FS48K 約0.006%

ひずみ率 FS48K 約0.006% ひずみ率 BPAS 約0.01%

ひずみ率 BPAS 約0.01%参考

2010/4 追記

電源ON直後に動作がおかしいと思われたら48K、96K SWを操作すると動作状態になります。

回路リセットが再度かかり動作開始します。

JP設定のSMをONにしてみてください。

もし、SW操作しても不動なら組立ミスがあると思われます。

ただし、JP SMをONにすると、無信号時の雑音が大幅に増えます。

雑音が気になるならOFFで使用するしかありません。

ON状態でも信号入力時、動作中の特性劣化はありません。

動作中に48K、96K SWを操作すると一瞬、小さなノイズが出る場合があります。

音楽再生中なら気にならない程度の小さなものです。

故障ではありません。

SW操作毎にAK4399をリセットしています。

AK4399はリセット状態でアナログ出力がハイインピーダンス状態となるので一瞬ノイズがでます。

2010/4/29

CPUプログラムを改良しました。

配布品よりVerUPしてます。(再送したCPUよりVerUPしてます)

ご自身でCPU書込みできる方はダウンロードして使用してください。

ただし、EM-DAC 4399Q購入者限定です。

ZIPで圧縮しています。解凍にはパスワードが必要です。

パスワードはメール件名に「EM-DAC 4399Q部品セットパスワード希望」と記載してメールしてください。

返信メールでパスワードをお知らせします。

注意 CPUへの書込みはご自身でおこなってください。

基板ISP端子とAVRプログラマーを接続して書込み可能です。

ダウンロード(パスワード発行)可能期間は、次回プログラム更新又はEM-DAC 4399Q相当次期品配布開始までとします。

EM-DAC 4399Q2配布開始にともない上記プログラム配布も終了しました。(2010/08)